平台概述

在本章中,我们将整体介绍 RTL8752H 平台,内容包括 硬件架构、软件系统 设计,以及如何使用 SDK 进行 应用程序开发。此外,本章还涵盖了 Boot 流程、中断管理 和 蓝牙应用 的基本工作原理等重要主题,以帮助开发者全面掌握平台资源,实现高效开发。

开发人员如果想快速上手 RTL8752H 开发板并运行第一个应用程序,可以访问 快速入门。

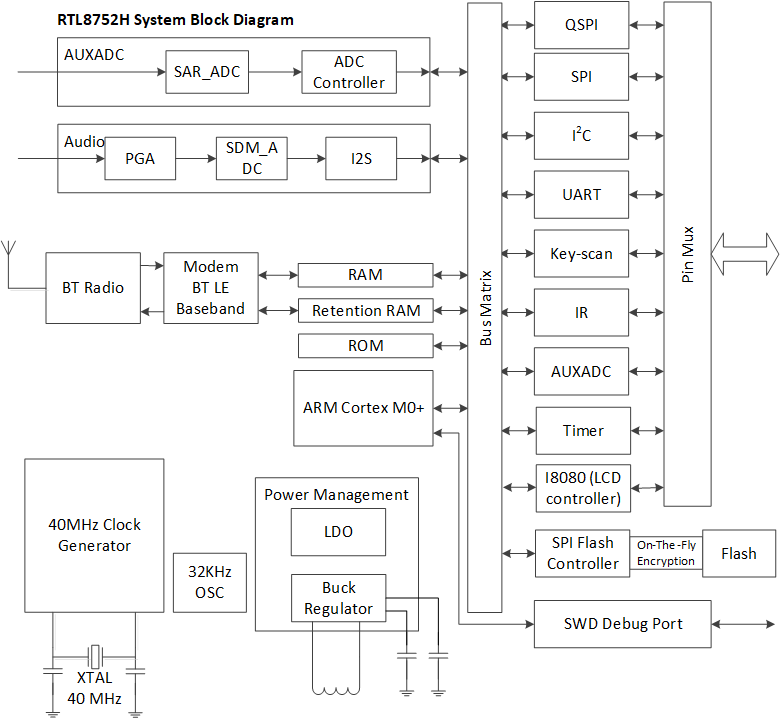

硬件架构

RTL8752H 的 CPU 为 Cortex-M0+(基于 ARMv6-M 架构),其最高主频可达 40MHz。

RTL8752H 硬件架构 主要由以下硬件单元组成:

丰富的外设

电源管理单元

时钟管理单元

RF 模块

RTL8752H 硬件架构

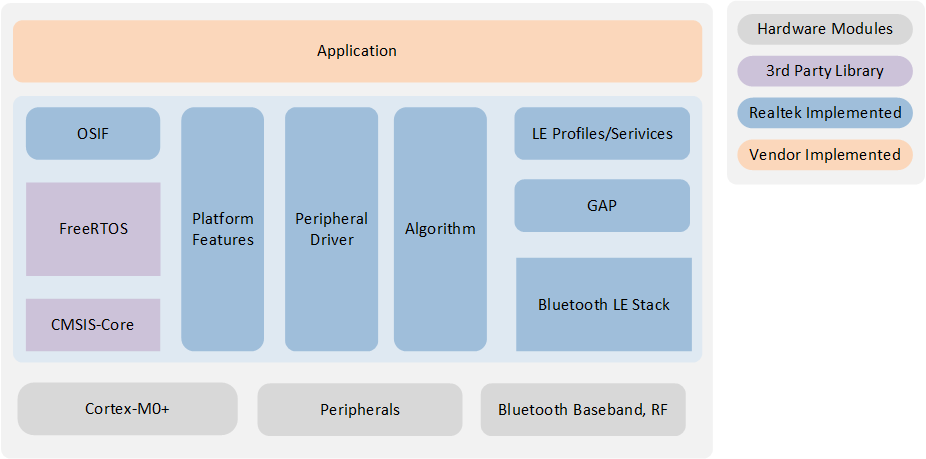

软件系统

软件架构

RTL8752H 软件架构 如下,主要有以下层级组成:

Platform Features: 包括 Flash Driver,Clock Manager,Power Manager,OTA 等。

Peripheral Driver: 提供应用层访问 RTL8752H 外设的接口。

Bluetooth LE Stack: Realtek 实现的 BT Controller 和 BT Host 层。

GAP: 应用程序和 BLE 协议栈交互的抽象层。

OSIF: Realtek 提供的实时操作系统的抽象层。

RTL8752H 软件架构

操作系统

RTL8752H 支持多种 RTOS,默认使用的是 FreeRTOS V10.4.4。

备注

RTL8752H 的 FreeRTOS 运行在 ROM 上。

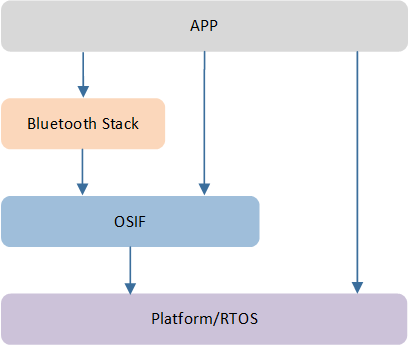

OSIF

OS Interface (OSIF) 是由 Realtek 抽象出来的通用 OS 接口层。OSIF 通过封装特定的 RTOS 接口来提供统一的接口。

使用 OSIF 的最大优势在于:开发者如果想要让上层应用运行在不同的 RTOS 上,可以将 OSIF 对接到相应 RTOS 上,而不需要对上层软件做任何修改。因此,我们也十分建议开发者在开发应用时使用 OSIF 接口,而不是直接访问特定 RTOS 的接口。

OSIF 架构

备注

OSIF 模块头文件请参考 inc/os/os_*.h。

任务

RTL8752H 的任务 是基于 FreeRTOS 设计的,默认支持抢占式线程。其任务优先级可以设置为 0~6,数字越大表示优先级越高。

系统默认创建的任务有:

FreeRTOS 默认创建:Timer Task、Idle Task

蓝牙协议栈默认创建:Bluetooth Controller Task、Bluetooth Host Task

应用程序可以根据实际的需求创建 Task,优先级建议设定在 1~4。

任务 |

说明 |

优先级 |

|---|---|---|

Timer |

FreeRTOS 用于实现软件定时器的任务 |

6 |

Bluetooth Controller |

蓝牙 HCI 层以下的协议栈实现 |

6 |

Bluetooth Host |

蓝牙 HCI 层以上的协议栈实现 |

5 |

APP |

应用层功能的实现 |

建议优先级为 1~4 |

Idle |

后台空闲任务,包括低功耗的处理 |

0 |

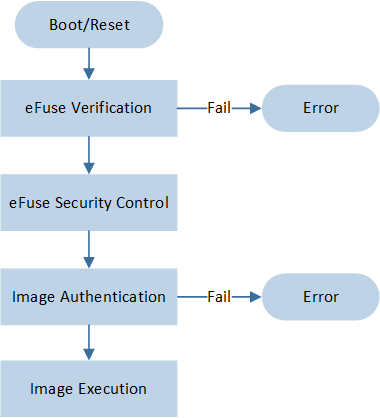

启动流程

RTL8752H 系统在上电或者重启时,都会执行启动流程,说明如下:

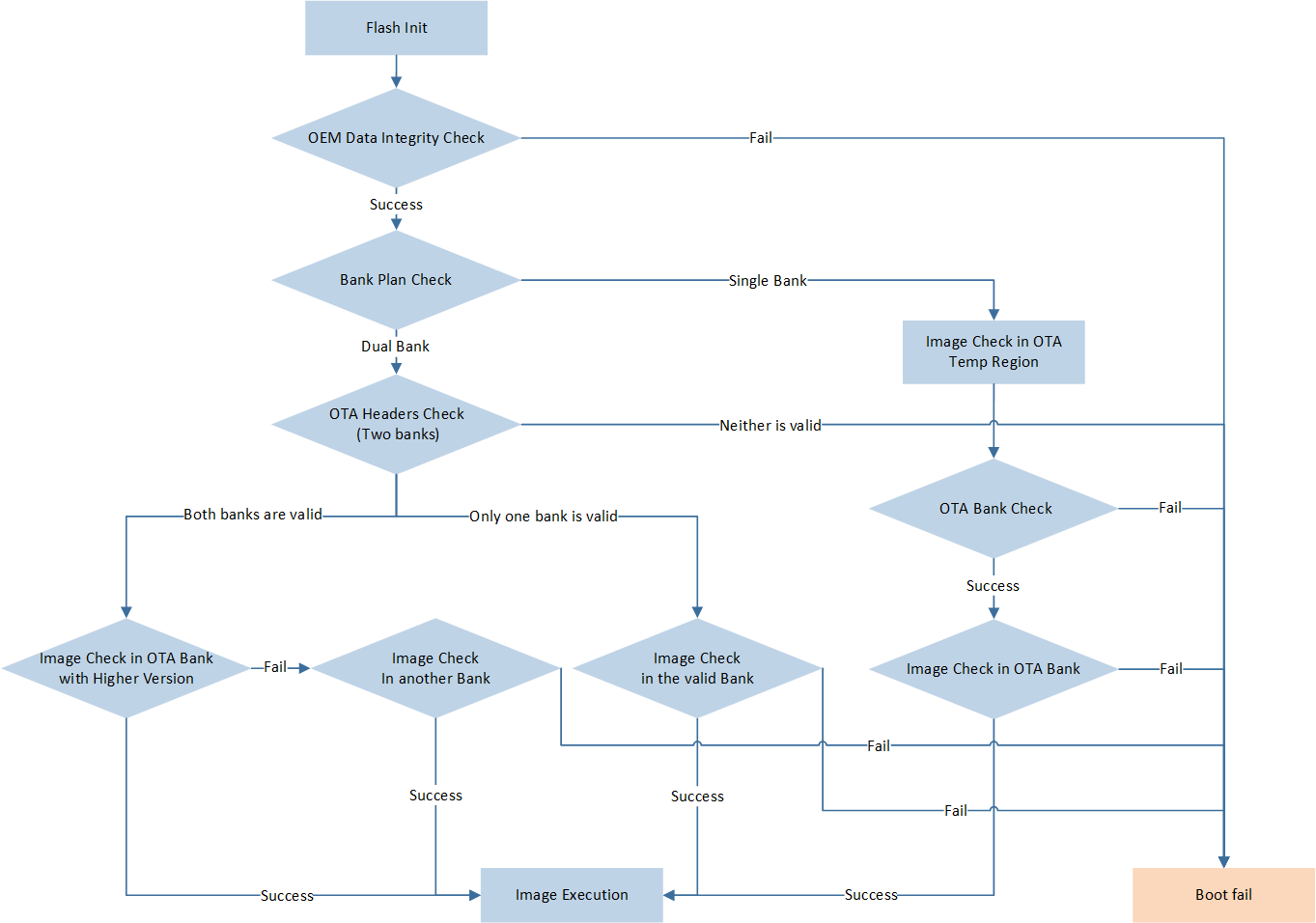

启动流程图

步骤 |

说明 |

|---|---|

eFuse 校验 |

对 eFuse 中的值进行校验,如果校验失败,则直接判定为 Boot 失败 |

安全控制 |

根据 eFuse 设定进行对应的安全控制,例如 SWD 是否打开、更新 Boot Config 设定等 |

Image 执行 |

Image 校验均通过后,按照设计的流程依次执行指定 Image |

Image 校验

RTL8752H 启动流程中的 Image 校验流程如下:

Image 校验流程

备注

OEM Data 又称作 Config File,其中包含了 RTL8752H 设定的重要参数,如 Image 的排布信息。

OTA 策略

RTL8752H 的 OTA 升级方案支持单 Bank 和双 Bank 两种方案。启动代码将根据 OEM Data 中的 Image 排布信息,判断出 OTA 升级的方案:

检查 Temp 区是否存在有效的待升级文件。如果有,则对其进行校验。若校验通过,则将其搬运到 Bank 中对应的位置。

校验 OTA Bank Header。

按顺序校验 OTA Bank 中的 Image。

执行指定的 Image。

-

校验两个 OTA Bank Header。根据校验结果,可分为以下三种情况:

情况一:两个 OTA Bank Header 校验都通过,则后续流程优先使用版本更新的 OTA Bank,另一个 OTA Bank 作为备份。

情况二:只有一个 OTA Bank Header 校验通过,则后续流程使用该 OTA Bank。

情况三:两个 OTA Bank Header 校验均未通过,则直接判定启动失败。

按顺序校验指定 OTA Bank 中的 Image。如果是情况一并且出现某个 Image 校验失败,系统会切到备份的 OTA Bank,并在该备份 Bank 中进行 Image 校验。

执行指定的 Image。

备注

OTA 相关说明请查阅 OTA 。

Image 排布相关说明请查阅 Image Layout。

校验方式

根据是否开启 Secure Boot 功能(eFuse 决定),Image 的校验方式可分为:

支持使用 SHA256 和 CRC16 完整性校验。

校验过程中,如果出现某个 Image 校验失败,系统仍会走后续的 Image Execution 流程,但会报出相关的 Error Log 以提示开发者。

支持使用 RSA 和 CMAC 签名验证。

校验过程中,如果出现某个 Image 校验失败,系统会中止执行后续的流程,进行 Error 处理。

Image 解密

Image 在校验成功后,会额外检查 Image 是否加密。如果 Image 加过密,则会将 Image 的加密区域和密钥等信息注册到 Flash On-The-Fly 引擎中。详情请查阅:安全机制。

存储

RTL8752H 的存储介质包括 ROM,RAM,Flash 和 eFuse,详情请查阅 Memory。

中断管理

RTL8752H 的中断管理基于 Cortex-M 的 NVIC (Nested Vectored Interrupt Controller) 系统,中断参数如下:

16 个 Cortex-M0+ 系统异常

32 个可屏蔽的中断通道(其中有两个中断有二级子中断)

4 个可编程的中断优先级

NVIC 和处理器内核接口紧密耦合,使得低延迟中断处理和高效处理晚抵达中断都成为可能。

中断向量表

中断向量表用于管理和处理不同类型的中断。它是存储在内存中的一个数据结构,包含了中断处理程序的入口地址。通过在中断向量表中存储中断处理程序的入口地址,系统可以快速定位并调用与中断类型相关的处理程序,从而提高系统的响应速度和效率。

RTL8752H 的中断向量表默认放置于 RAM 中划分的一块区域上。开发者可通过 API RamVectorTableUpdate() 来更新中断向量表中指定的 ISR。

Exception Number |

CMSIS-CORE enumeration value |

Exception Type |

Description |

|---|---|---|---|

1 |

Reset |

Reset |

|

2 |

[-14] |

NMI |

Non-Maskable Interrupt The Watchdog is linked to the NMI vector |

3 |

[-13] |

HardFault |

Fault handling exception |

4 ~ 10 |

Reserved |

||

11 |

[-5] |

SVCall |

Supervisor call via SVC instruction |

12~13 |

Reserved |

||

14 |

[-2] |

PendSV |

Pendable request for system service |

15 |

[-1] |

SysTick |

System Tick Timer |

16 |

[0] |

System Interrupt |

Interrupt the CPU when the system is awakened by a GPIO event |

17 |

[1] |

Internal use |

Internal use |

18 |

[2] |

BT MAC |

BT MAC Interrupt |

19 |

[3] |

Timer3 |

Timer3 Global Interrupt |

20 |

[4] |

Timer2 |

Timer2 Global Interrupt |

21 |

[5] |

Internal use |

Internal use |

22 |

[6] |

I2S0_TX |

I2S0 TX Interrupt |

23 |

[7] |

I2S0_RX |

I2S0 RX Interrupt |

24 |

[8] |

Timer4_5 |

Timer4~5 interrupt has secondary interrupts. Refer to Timer4~5 Interrupt. |

25 |

[9] |

ZIGBEE |

ZIGBEE Interrupt |

26 |

[10] |

PF_RTC |

Platform RTC Interrupt |

27 |

[11] |

RTK_UART0 |

RTK UART0 Interrupt |

28 |

[12] |

RTK_UART1 |

RTK UART1 Interrupt |

29 |

[13] |

I8080 |

I8080 Interrupt |

30 |

[14] |

SPI0 |

SPI 0 Interrupt |

31 |

[15] |

SPI1 |

SPI 1 Interrupt |

32 |

[16] |

I2C0 |

I2C 0 Interrupt |

33 |

[17] |

I2C1 |

I2C 1 Interrupt |

34 |

[18] |

ADC |

ADC Global Interrupt |

35 |

[19] |

Peripheral |

Peripheral interrupt has secondary interrupts. Refer to Peripheral Interrupt. |

36 |

[20] |

DMA_Channel0 |

RTK-DMA channel0 Global Interrupt |

37 |

[21] |

DMA_Channel1 |

RTK-DMA channel1 Global Interrupt |

38 |

[22] |

DMA_Channel2 |

RTK-DMA channel2 Global Interrupt |

39 |

[23] |

DMA_Channel3 |

RTK-DMA channel3 Global Interrupt |

40 |

[24] |

Enhanced_Timer0 |

Enhanced Timer 0 Interrupt |

41 |

[25] |

Enhanced_Timer1 |

Enhanced Timer 1 Interrupt |

42 |

[26] |

GPIO_Group3 |

|

43 |

[27] |

GPIO_Group2 |

|

44 |

[28] |

IR |

IR module global Interrupt |

45 |

[29] |

GPIO_Group1 |

|

46 |

[30] |

GPIO_Group0 |

|

47 |

[31] |

RTK_UART2 |

RTK UART 2 Interrupt |

Exception Number |

Exception Type |

Description |

|---|---|---|

48 |

Timer4 |

Timer4 Interrupt |

49 |

Timer5 |

Timer5 Interrupt |

Exception Number |

Exception Type |

Description |

|---|---|---|

50 |

SPIC0 |

SPIC0 Flash Interrupt |

51 |

Qdecode |

Qdecode Global Interrupt |

52 |

Keyscan |

Keyscan Global Interrupt |

53 |

SPI2W |

2-wire/3-wire SPI Interrupt |

54 |

LPCOMP |

Analog Comparator Interrupt |

55 |

PTA_Mailbox |

MailBox Interrupt |

56 |

SPIC1 |

SPIC1 Flash Interrupt |

57 |

SHA256 |

SHA256 Interrupt |

58 |

Platform |

Platform Interrupt |

59 |

TRNG |

TRNG Interrupt |

61 |

FLASH_SEC |

Flash On-The-Fly Interrupt |

62 |

RTC |

Real Time Counter Interrupt |

63 |

WDT |

Watchdog Global Interrupt |

GPIO Group 3 Interrput |

GPIO Group 2 Interrput |

GPIO Group 1 Interrput |

GPIO Group 0 Interrput |

|---|---|---|---|

GPIO3 |

GPIO2 |

GPIO1 |

GPIO0 |

GPIO7 |

GPIO6 |

GPIO5 |

GPIO4 |

GPIO11 |

GPIO10 |

GPIO9 |

GPIO8 |

GPIO15 |

GPIO14 |

GPIO13 |

GPIO12 |

GPIO19 |

GPIO18 |

GPIO17 |

GPIO16 |

GPIO23 |

GPIO22 |

GPIO21 |

GPIO20 |

GPIO27 |

GPIO26 |

GPIO25 |

GPIO24 |

GPIO31 |

GPIO30 |

GPIO29 |

GPIO28 |

中断优先级

RTL8752H 使用的 ARMv6-M 架构可支持的中断优先级是 4 个。但为了与 Realtek Bee 系列的其他 SoC 保持兼容(大多数支持 8 个优先级),RTL8752H 的 Irq-Priority-Bits-Number 被设定为 3, 因此中断优先级有如下关系: (0 = 1) > (2 = 3) > (4 = 5) > (6 = 7) 。

优先级的设定推荐遵循以下规则:

优先级 |

规则 |

|---|---|

0/1 |

用于实时性要求非常高的中断,BT MAC Interrupt 默认使用该优先级 |

|

2/3 4/5 |

一般用于普通的外设中断 |

6/7 |

SysTick 和 PendSV |

备注

RTL8752H 使用的 ARMv6-M 架构不支持动态调整中断的优先级。如果中断优先级要调整,需要先关闭中断,修改中断优先级,再重新使能中断。

功耗模式

RTL8752H 支持以下四种功耗模式:

功耗模式 |

说明 |

|---|---|

CPU Active |

系统处于完全的供电和活跃状态 |

CPU Sleep |

系统进入 wfi 状态,此模式下 CPU clock 会自动降速 |

系统进入较低的功耗模式,系统进入休眠模式,以及较快的进出时间,同时 RAM 内容保持 |

|

Power Down |

系统进入极致的低功耗模式,此模式下 RAM 内容不保持,从Power Down 模式退出会执行重启流程,较 DLPS 模式的退出耗时更长 |

RTL8752H 会在满足特定的条件时进入特定的功耗模式,并在符合特定条件下唤醒系统。详情请查阅 低功耗模式。

应用程序开发

SDK 目录

在应用程序开发之前,请先熟悉 RTL8752H 的 SDK,目录结构如下:

└── SDK

├── bin 存放编译生成的可执行文件或二进制文件

├── board 包含一些示例项目,开发者可以通过这些项目了解如何在该评估板上开发应用程序

├── evb

└── samples

├── doc 保存 SDK 相关的文档资料

├── inc 包含各种头文件,分为以下子目录

├── app 应用程序相关的头文件,定义了应用程序层次的接口

├── bluetooth 与蓝牙功能相关的头文件,包括蓝牙协议栈、配置等

├── os 操作系统相关的头文件,包含 OSIF 和 FreeRTOS 的接口定义

├── peripheral 外设相关的头文件,如 GPIO、UART、SPI、I2C 等

└── platform 平台相关的头文件,定义了平台级别的接口和配置

├── src 包含实现具体功能的源文件(.c, .s等)

└── tools 包含用于编译、烧录、调试的工具和脚本

示例工程

为了帮助开发者快速上手开发应用程序,RTL8752H SDK中 已经创建好了许多示例工程。详情请参考 示例工程。

备注

由于示例工程可能会随着 SDK 一起更新。为了更好地使用最新的示例代码,建议把新增的代码以模块化的形式组织。

组织结构

以 ble_peripheral 的 Keil 工程为例,分为以下几个模块来组织源文件:

工程目录 |

说明 |

|---|---|

Include |

存放 ROM UUID 文件 |

CMSIS |

存放启动代码 |

Lib |

应用程序使用的所有二进制文件 |

Peripheral |

应用程序使用的所有外设驱动和模块代码 |

Profile |

应用程序使用的 BLE Profiles 或者服务 |

APP |

BLE Peripheral 应用的实现 |

通用文件

RTL8752H SDK 的示例工程中均包含以下通用文件:

文件 |

说明 |

|---|---|

|

UUID 头文件是 Application 用来识别 ROM 的,无需更改 |

|

ROM 符号库,应用程序链接 ROM 中的符号 |

|

lowerstack 链接 ROM 中的符号 |

|

Realtek 拓展功能的库 |

|

实现 BLE 功能的 GAP 库 |

|

RTL8752H 应用程序启动的汇编文件 |

|

RTL8752H 应用程序启动的 C 文件 |

|

配置引脚和低功耗模式的头文件 |

|

Flash 布局文件,此文件由 Flashmap Generate Tool 工具生成 |

|

Memory 配置相关的文件 |

APP 工作原理

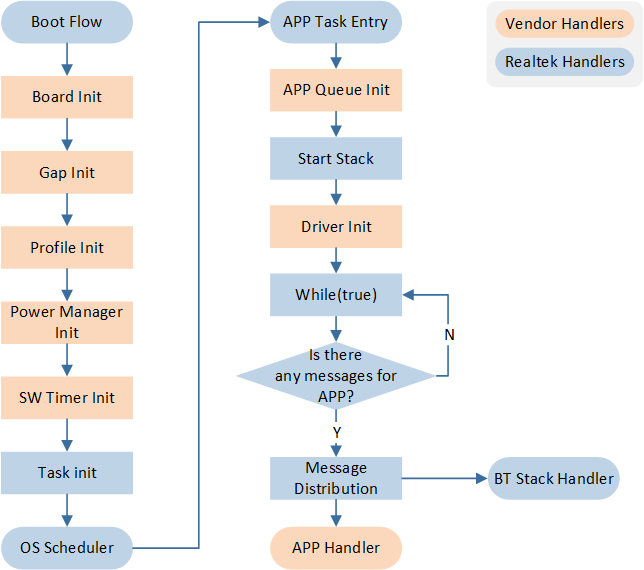

RTL8752H SDK 内提供的 BLE 示例应用程序的执行流程如下:

BLE APP 执行流程

初始化

BLE 应用是在 main() 函数中开始进行初始化的,各初始化步骤的含义如下:

步骤 |

说明 |

|---|---|

Board Init |

PINMUX 和 PAD 初始化设置 |

Gap Init |

GAP 相关参数的初始化 |

Profile Init |

BLE Profiles 的初始化 |

Power Manager Init |

电源管理相关的初始化 |

SW Timer Init |

软件定时器的初始化 |

APP Queue Init |

APP Queue 的初始化,包括 IO MSG Queue 和 Event Queue |

Driver Init |

外设的初始化 |

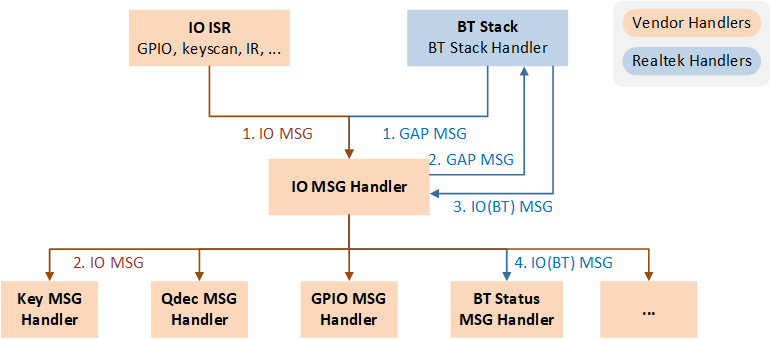

消息和事件处理机制

BLE 应用中,蓝牙协议栈和外设都是通过 消息和事件处理机制 与 APP 层进行交互的。

消息和事件处理机制的本质是消息(IO MSG)会被封装成事件(Event),这些 Event 则会在 APP 层的消息处理器中被分发处理,具体说明如下:

消息和事件处理机制

如上图所示,原始消息被封装成 Event 后,会发送至对应的 queue 中。APP 层的消息分发器在收到 Event 后,基于 Event 类别调用对应的MSG Handler 处理:

如果 Event 类型是 IO MSG: 被消息分发器转发给特定 IO MSG Handler 处理。

如果 Event 类型是 来自蓝牙协议栈的MSG: 先被消息分发器转发给 BT 状态机,BT 状态机处理完 MSG 后,再封装成 BT IO MSG 发送至 queue 中。

开发者在开发应用程序时,需要负责以下事项:

实现外设的 ISR,在 ISR 中完成初步处理,如果需要进一步处理则封装 Event 发给 APP。

根据需求扩展消息分发器,以便接收和处理用户定义的 MSG。

实现应用层相关的 MSG Handler。

根据需求扩充自定义 Message Type 和 Subtype。

备注

此部分的具体实现请参考示例工程里的

app_task.c和app_flag.h。GAP 层通知 APP 层是通过消息和事件处理机制,而 APP 层可以直接调用 GAP 层的 APIs 来通知 GAP 层。

Pin 设定

引脚的设定在 board.h 中定义。

#define KEY_0 P4_0

#define BEEP P4_1

#define LED_0 P2_1

#define LED_1 P2_4

功耗模式设定

在示例工程中,开发者可以透过 Realtek 预设的宏定义来控制是否打开低功耗模式:

绝大部分工程:

board.h中的宏DLPS_EN用于控制是否进入低功耗模式。BLE 相关工程:

app_flags.h中的宏F_BT_DLPS_EN用于控制是否进入低功耗模式。

详情请查阅 低功耗模式 。

调试

调试应用程序有以下两种方式:

使用 Log 机制跟踪代码的执行和数据。

使用 Keil MDK 或 J-Link Commander 和 SWD 进行调试,增加/删除断点以及访问/追踪 memory 等。

详情请查阅 调试指南。

See Also

相关 API Reference 请查看: