IO

This document is intended to help beginners quickly become familiar with the peripherals of RTK MCU. It introduces various peripherals, including PINMUX, PAD, GPIO, TIMER, PWM, UART, GDMA, I2C, SPI, IR, RTC, LPC, 3-wire SPI, CapTouch, ADC, QDEC, KeyScan, SLEEP LED, I2S, SDIO peripherals. Additionally, this document covers an IO demo project, peripheral functions and features, hardware-related knowledge, peripheral operation flow, and corresponding demo code.

Each chapter is mainly divided into the following aspects to introduce peripherals.

Peripheral function description

Peripheral feature description

Introduction to hardware protocols

Basic hardware information of peripherals

Operation flow

Sample code description

Requirements

The sample supports the following development kits:

Hardware Platforms |

Board Name |

Build Target |

|---|---|---|

RTL87x3E HDK |

RTL87x3E EVB |

io_demo_2M_bank0 |

RTL87x3D HDK |

RTL87x3D EVB |

io_demo_16M_bank0 |

RTL87x3EP HDK |

RTL87x3EP EVB |

io_demo_4M_bank0 |

When built for an xxx_2M_xxx build target, the sample is configured to compile and run with a 2M flash map.

When built for an xxx_4M_xxx build target, the sample is configured to compile and run with a 4M flash map.

When built for an xxx_16M_xxx build target, the sample is configured to compile and run with a 16M flash map.

To quickly set up the development environment, please refer to the detailed instructions provided in Quick Start.

Configurations

Users can modify the macro definitions shown below in the sample code to configure the pins used in the example. For specific pin definitions, please refer to the list below:

#define UART_TX_PIN P3_1

#define UART_RX_PIN P3_0

#define UART_CTS_PIN P0_0

#define UART_RTS_PIN P0_1

Building and Downloading

The detailed information about building and downloading can be found in Building and Downloading.

This sample can be found under board\evb\io_demo in the SDK folder structure.

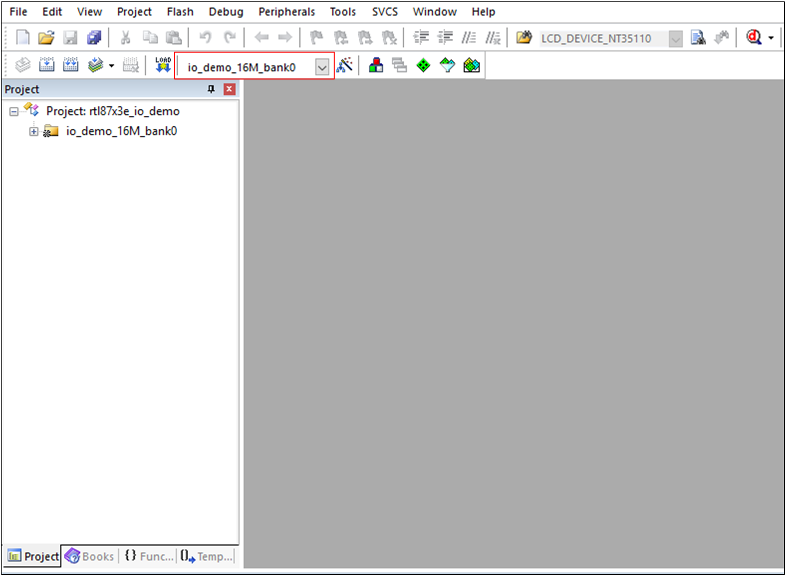

Take the project rtl87x3e_io_demo.uvprojx and target io_demo_16M_bank0 as an example, to build and run the sample with the Keil development environment. Follow the steps listed below:

Open

rtl87x3e_io_demo.uvprojx.Choose the build target

io_demo_16M_bank0.

Build the target.

After a successful compilation, the APP bin file

io_demo_bank0_MP-v0.0.0.0-xxx.binwill be generated in the directorybin\rtl87x3e\flash_16M\bank0.Download the generated APP bin

io_demo_bank0_MP-v0.0.0.0-xxx.bininto the EVB board.Press the reset button on the EVB board.

Experimental Verification

The detailed test procedure can be found in the list below:

Code Overview

The IO demo application overview will be introduced according to the following parts:

The IO demo project overview will be introduced in the chapter Source Code Directory.

The IO demo project source code overview will be introduced in the chapter Source Code Overview.

Source Code Directory

IO demo project shows how to use peripherals to communicate with other devices. A specific peripheral and its usage scenario can be changed to demonstrate, with its source files added to the build target and its demo functions called in main().

This section describes the project directory and project structure. The reference files directory is as follows:

Project directory:

board\evb\io_demo.Project source code directory:

src\sample\io_demo.

Source files in the sample project are currently categorized into several groups as below.

└── Project: io_demo_16M_bank0

├── include ROM UUID header files. Users do not need to modify it.

├── lib Includes all binary symbol files that user application is built on.

├── cmsis The cmsis source code. Users do not need to modify it.

├── io_driver The IO driver code. Users do not need to modify it.

├── io_hal The IO HAL layer code. Users do not need to modify it.

├── app The application source code.

├── adc The ADC demo source code.

├── gdma The GDMA demo source code.

├── gpio The GPIO demo source code.

├── i2c The I2C demo source code.

├── ir The IR demo source code.

├── keyscan The KeyScan demo source code. RTL87x3EP doesn’t support it.

├── led The LED demo source code.

├── lpc The LPC demo source code.

├── qdec The QDEC demo source code.

├── rtc The RTC demo source code.

├── sdio The SDIO demo source code.

├── spi The SPI demo source code.

├── spi3w The 3-wire SPI demo source code. Only RTL87x3D supports it.

├── tim The TIMER and PWM demo source code.

├── uart The UART demo source code.

├── ctc The CapTouch demo source code. Only RTL87x3E supports it.

├── i2s The I2S demo source code.

├── dlps The DLPS demo source code.

└── spi_external_flash The SPI external flash demo source code.

Source Code Overview

This section describes some parts of the source code used in the application of this project.

Initialization

The main function is invoked when the application is powered on or the chip is reset, and it performs the following initialization functions:

RAM_TEXT_SECTION

int main(void)

{

__enable_irq();

WDG_Disable();

IO_PRINT_INFO0("Hello io demo !");

extern void gpio_int_demo(void);

gpio_int_demo();

os_sched_start();

}

The gpio_int_demo() function can be replaced by the demo entry function in the demo files, such as adc_demo() in the adc_demo.c file. Note that each demo entry function is independent of each other.

Initialization Flow

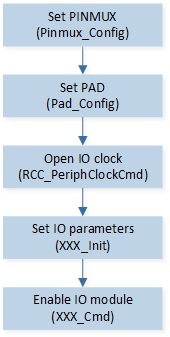

Peripheral initialization mainly consists of the following components:

Set peripheral PINMUX and PAD.

Enable peripheral clock signal.

Set peripheral initialization parameters.

Enable peripheral.

The initialization procedure is shown in the following figure, where ‘XXX’ is the name of the peripheral to be initialized, such as GPIO, I2C, or SPI.

Clock Configuration

Enable GPIO clock by calling RCC_PeriphClockCmd() function.

RCC_PeriphClockCmd(APBPeriph_GPIO, APBPeriph_GPIO_CLOCK, ENABLE);

PINMUX Configuration

Configure PINMUX status of the pin by calling Pinmux_Config() function.

/* Configure Pin P0_5 as GPIO function */

Pinmux_Config(P0_5, DWGPIO);

For optional pin values and map GPIO please reference the file below.

RTL87x3E: inc\rtl87x3e\platform\rtl876x.h

RTL87x3D: inc\rtl87x3d\platform\pin_def.h

RTL87x3EP: inc\rtl87x3ep\platform\pin_def.h

PAD Configuration

Configure the PAD status of the pin by calling Pad_Config() function.

Pad_Config(P0_5, PAD_PINMUX_MODE, PAD_IS_PWRON, PAD_PULL_NONE, PAD_OUT_ENABLE, PAD_OUT_HIGH);

Interrupt Configuration

Enable IRQ interrupt by calling NVIC_Init() function.

NVIC_InitTypeDef NVIC_InitStruct;

NVIC_InitStruct.NVIC_IRQChannel = GPIO5_IRQ;

NVIC_InitStruct.NVIC_IRQChannelPriority = 5;

NVIC_InitStruct.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStruct);

Initialize Peripheral

Initialize the peripheral by calling XXX_Init for each peripheral, and ‘XXX’ is the name of the peripheral to be initialized.

GPIOx_Init();

Disable Peripheral

Disable the peripheral by calling XXX_DeInit for each peripheral, and ‘XXX’ is the name of the peripheral to be disabled.

GPIOx_DeInit();

PINMUX and PAD

PAD Demo Code Support List

Demo 1 |

dlps_gpio_wk_demo.c |

|---|---|

Sample Purpose |

Demonstrates how PAD wakes up the system from DLPS mode. |

Brief Introduction |

This sample code demonstrates how PAD wakes up the system. |

File Path |

|

Function Entry |

|

Pin Definition |

|

Hardware Connection |

When the system needs to be woken up, connect M0_0 to GND on EVB. |

Expected Result |

1. Press the reset button on the EVB, the string ‘dlps_store: enter dlps’ will be printed in Debug Analyzer, and the system will enter DLPS mode. |

Function Description

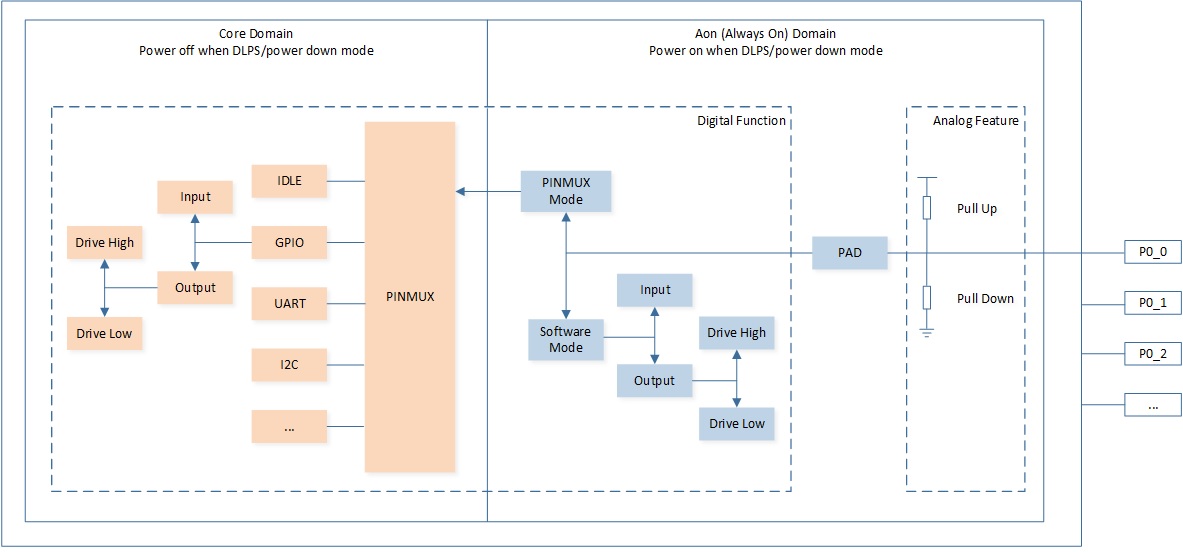

PINMUX is an abbreviation for pin multiplexing. Because the SoC has a limited number of pins, pin multiplexing allows the SoC to use the limited pins for various functions, such as SPI, I2C, and GPIO.

PAD is used to control the behavior of a pin, such as pull-up or pull-down, output high or low level, and wake-up functions.

As shown in the figure below. The PINMUX circuit and IO modules are in the core domain and will be powered down during low power mode, so they cannot work during low power mode. The PAD circuit is in the AON domain and will not be powered down during low power mode, so the PAD can work normally during low power mode. The PAD is mainly used to maintain the pin output state or wake up the system in low power mode.

The PAD can be configured as PINMUX mode and software mode. Only when the PAD is set to PINMUX mode, can this pin be connected to the core domain to achieve pin multiplexing.

PAD Feature List

Two operating modes: PINMUX mode and software mode.

Configurable pin pull-up or pull-down resistors.

Configurable pin independently output high or low level in software mode.

Keep power during DLPS/power down mode, powered off in ship mode.

Wake up the system from DLPS and power down mode from high or low triggers on all the pins.

Hybrid PAD Usage

The Hybrid PAD can be configured in digital mode or analog mode. Configure the mode of the hybrid PAD by calling Pad_AnalogMode() function.

/* Configure MIC1_P as analog mode */

Pad_AnalogMode(MIC1_P, PAD_ANALOG_MODE);

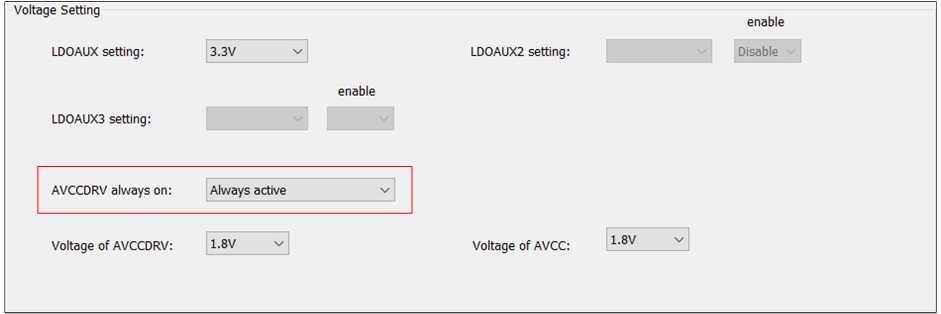

When the hybrid PAD is configured in digital mode (GPIO, I2C, etc), the ‘AVCCDRV always on’ option needs to be configured as ‘Always active’ on the MCUConfig Tool.

Note

RTL87x3D hybrid PAD: LOUT_N, P_UART, ROUT_N, ROUT_P, MIC1_N, MIC1_P, MIC2_N, MIC2_P, MIC3_N, MIC3_P, MIC4_N, MIC4_P, MIC5_N, MIC5_P, MIC6_N, MIC6_P, AUX_R, AUX_L, MICBIAS.

RTL87x3E hybrid PAD: AUX_R, AUX_L, MIC1_P, MIC1_N, MIC2_P, MIC2_N, MICBIAS, LOUT_P, LOUT_N, ROUT_P, ROUT_N, MIC3_P, MIC3_N.

RTL87x3EP hybrid PAD: DAOUT_P, DAOUT_N, MIC1_P, MIC1_N, MIC2_P, MIC2_N, MICBIAS.

GPIO

GPIO Demo Code Support List

Demo 1 |

gpio_input_demo.c |

|---|---|

Sample Purpose |

Demonstrates GPIO input mode. |

Brief Introduction |

This sample code demonstrates how to get the input level value of GPIO. |

File Path |

|

Function Entry |

|

GPIO Direction |

Input mode |

Pin Definition |

|

Expected Result |

Press the reset button on the EVB, the string ‘gpio_test: gpio_value 1’ will be printed in Debug Analyzer. |

Demo 2 |

gpio_output_demo.c |

|---|---|

Sample Purpose |

Demonstrates GPIO output mode. |

Brief Introduction |

This sample code demonstrates how to use GPIO to output high and low levels. |

File Path |

|

Function Entry |

|

GPIO Direction |

Output mode |

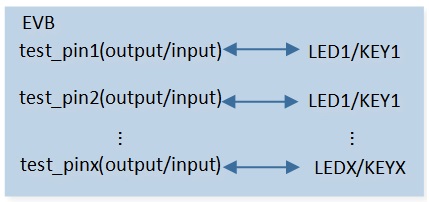

Hardware Connection |

As shown in GPIO Hardware Connection Diagram. On EVB, connect P0_1 and LED1, and connect P0_2 and LED2. |

Pin Definition |

|

Expected Result |

Press the reset button on the EVB. LED1 and LED2 will light up or off when the output level is selected as high or low. |

Demo 3 |

gpioab_output_demo.c |

|---|---|

Sample Purpose |

Demonstrates GPIOx output mode whether the pin belongs to GPIOA or B. |

Brief Introduction |

This sample code demonstrates the GPIOx output function. The output level value can be detected by connecting with LED. |

File Path |

|

Function Entry |

|

GPIO Direction |

Output mode |

Hardware Connection |

As shown in GPIO Hardware Connection Diagram. On EVB, connect P4_3 and LED1. |

Pin Definition |

|

Expected Result |

Press the reset button on the EVB. LED1 will light up or off when the gpio_pin_bit is selected to Set or Reset. |

Demo 4 |

gpioab_output_group_demo.c |

|---|---|

Sample Purpose |

Demonstrates GPIOx group output mode whether the pins belong to GPIOA or B. |

Brief Introduction |

This sample code demonstrates the GPIOx group output function. These output level values can be detected by connecting with LED. |

File Path |

|

Function Entry |

|

GPIO Direction |

Output mode |

Hardware Connection |

As shown in GPIO Hardware Connection Diagram. On EVB, connect LED and test pin. |

Expected Result |

Press the reset button on the EVB. The LED will light up or off when the gpio_pin_bit is selected to Set or Reset. |

Demo 5 |

gpio_int_demo.c |

|---|---|

Sample Purpose |

Demonstrates GPIO used as a key by edge trigger mode with hardware debounce. |

Brief Introduction |

This sample code demonstrates the detection of GPIO input through interrupt. When the button is pressed (such as P1_0 changing from high level to low level), the falling edge of GPIO is detected, and the GPIO interrupt is triggered. Then switch the edge trigger, after the button is released (P1_0 changes from low level to high level), the GPIO interrupt is triggered again. |

File Path |

|

Function Entry |

|

GPIO Direction |

Input mode |

Hardware Connection |

As shown in GPIO Hardware Connection Diagram. On EVB, connect P1_0, P1_1, P2_1, P2_2 to KEY1 ~ KEY4 respectively. |

Pin Definition |

|

Expected Result |

Press the reset button on the EVB. Press KEY1 ~ KEY4: string ‘gpio_isr_cb: pin_name P1_0, gpio_level 0’ ‘gpio_isr_cb: pin_name P1_1, gpio_level 1’ ‘gpio_isr_cb: pin_name P2_1, gpio_level 0’ ‘gpio_isr_cb: pin_name P2_2, gpio_level 1’ will be printed in Debug Analyzer. Release KEY1 ~ KEY4: string ‘gpio_isr_cb: pin_name P1_0, gpio_level 1’ ‘gpio_isr_cb: pin_name P1_1, gpio_level 0’ ‘gpio_isr_cb: pin_name P2_1, gpio_level 1’ ‘gpio_isr_cb: pin_name P2_2, gpio_level 0’ will be printed in Debug Analyzer. |

Demo 6 |

pad_int_demo.c |

|---|---|

Sample Purpose |

Demonstrates PAD interrupt mode to realize key detection. |

Brief Introduction |

This sample code demonstrates key detection by PAD interrupt mode. When the button is pressed (such as P1_0 changing from high level to low level), the low level of the pin is detected, and the system handler is triggered. Then switch the level trigger, after the button is released (P1_0 changes from low level to high level), the system handler is triggered again. |

File Path |

|

Function Entry |

|

GPIO Direction |

Input mode |

Hardware Connection |

As shown in GPIO Hardware Connection Diagram. On EVB, connect P1_0, P1_1, P2_1, P2_2 to KEY1 ~ KEY4 respectively. |

Pin Definition |

|

Expected Result |

Press the reset button on the EVB. Press KEY1: string ‘system_handler: pin0 interrupt triggered, pin_0_state 0’ will be printed in Debug Analyzer. Release KEY1: string ‘system_handler: pin0 interrupt triggered, pin_0_state 1’ will be printed in Debug Analyzer. |

Demo 7 |

gpio_key.c |

|---|---|

Sample Purpose |

Demonstrates GPIO used as a key by level trigger mode with TIMER debounce. |

Brief Introduction |

This sample code demonstrates the detection of GPIO input through interrupt. When the button is pressed (P0_0 changes from high level to low level), the low level of GPIO is detected, and the GPIO interrupt is triggered. Then restart the TIMER in the GPIO handler, after the 30ms debounce time, enter the TIMER handler to switch the level trigger, when the button is released (P1_0 changes from low level to high level), the GPIO interrupt is triggered again. Then the TIMER restarts again. |

File Path |

|

Function Entry |

|

GPIO Direction |

Input mode |

Hardware Connection |

As shown in GPIO Hardware Connection Diagram. On EVB, connect P0_0 and KEY1. |

Pin Definition |

|

Expected Result |

Press the reset button on the EVB. Press KEY1: string ‘key_handler: key_status 0’ ‘debounce_hw_timer_callback: Key press’ will be printed in Debug Analyzer. Release KEY1: string ‘key_handler: key_status 1’ ‘debounce_hw_timer_callback: Key release’ will be printed in Debug Analyzer. |

Demo 8 |

gpio_edge_key.c |

|---|---|

Sample Purpose |

Demonstrates GPIO used as a key by edge trigger mode with hardware debounce. |

Brief Introduction |

This sample code demonstrates the detection of GPIO input through interrupt. When the button is pressed (P0_0 changes from high level to low level), the falling edge of GPIO is detected, and the GPIO interrupt is triggered. Then switch the edge trigger, after the button is released (P0_0 changes from low level to high level), the GPIO interrupt is triggered again. |

File Path |

|

Function Entry |

|

GPIO Direction |

Input mode |

Hardware Connection |

As shown in GPIO Hardware Connection Diagram. On EVB, connect P0_0 and KEY1. |

Pin Definition |

|

Expected Result |

Press the reset button on the EVB. Press KEY1: string ‘key_handler: Key press’ will be printed in Debug Analyzer. Release KEY1: string ‘key_handler: Key release’ will be printed in Debug Analyzer. |

Demo 9 |

dma_tim_demo.c |

|---|---|

Sample Purpose |

Demonstrates how GDMA controls GPIO output. |

Brief Introduction |

This sample code demonstrates how to use TIMER to toggle GDMA to control GPIO to output high and low levels of specified lengths. |

File Path |

|

GPIO Direction |

Output mode |

GDMA Direction |

Memory to Peripheral |

Function Entry |

|

Pin Definition |

|

Expected Result |

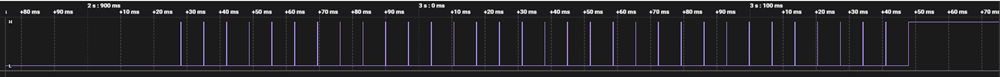

Press the reset button on the EVB. Use a Logic Analyzer to capture the waveform of P0_2, and the output waveform results of single-block or multi-block are shown in GPIO GDMA Result Diagram. |

Function Description

The GPIO integrated core is programmable general-purpose input/output. Each GPIO pin can be configured by software as an output, input, or interrupt peripheral function.

Feature List

32 independently configured GPIO signals in every port, with independently controllable signal bits.

Support hardware and software control.

Support input and output control.

Support level-triggered and edge-triggered interrupts.

Support low and high level-triggered interrupts.

Support rising and falling edge-triggered interrupts.

Support both-edge-triggered interrupts.

Support hardware debounce function.

Support GPIO+TIMER+GDMA function.

Note

RTL87x3D supports 3 ports. RTL87x3E and RTL87x3EP support 2 ports.

When the GPIO is controlled by GDMA, it should be configured in hardware mode.

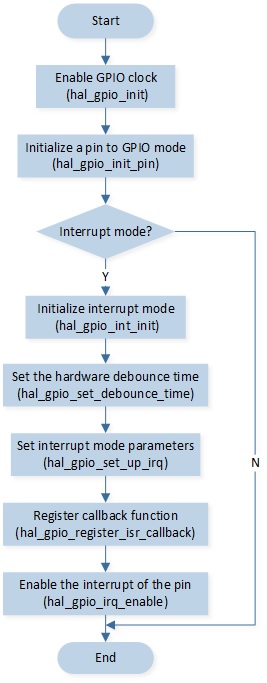

GPIO Initialization Flow

The GPIO initialization flow is shown in the following figure.

Input Mode

The codes below demonstrate the operation flow of GPIO in input mode.

hal_gpio_init();

hal_gpio_init_pin(TEST_Pin, GPIO_TYPE_AUTO, GPIO_DIR_INPUT, GPIO_PULL_UP);

gpio_value = hal_gpio_get_input_level(TEST_Pin);

Output Mode

The codes below demonstrate the operation flow of GPIO in output mode.

hal_gpio_init();

hal_gpio_init_pin(TEST_PIN, GPIO_TYPE_CORE, GPIO_DIR_OUTPUT, GPIO_PULL_UP);

hal_gpio_init_pin(TEST_PIN_2, GPIO_TYPE_AON, GPIO_DIR_OUTPUT, GPIO_PULL_UP);

for (uint16_t i = 0; i < 10; i++)

{

hal_gpio_set_level(TEST_PIN, GPIO_LEVEL_LOW);

hal_gpio_set_level(TEST_PIN_2, GPIO_LEVEL_LOW);

hal_gpio_set_level(TEST_PIN, GPIO_LEVEL_HIGH);

hal_gpio_set_level(TEST_PIN_2, GPIO_LEVEL_HIGH);

}

Interrupt Mode

The codes below demonstrate the operation flow of GPIO in interrupt mode.

hal_gpio_init();

hal_gpio_int_init();

hal_gpio_set_debounce_time(30);

hal_gpio_init_pin(GPIO_DEMO_INPUT_PIN0, GPIO_TYPE_AUTO, GPIO_DIR_INPUT, GPIO_PULL_UP);

hal_gpio_init_pin(GPIO_DEMO_INPUT_PIN1, GPIO_TYPE_AUTO, GPIO_DIR_INPUT, GPIO_PULL_DOWN);

hal_gpio_init_pin(GPIO_DEMO_INPUT_PIN2, GPIO_TYPE_AUTO, GPIO_DIR_INPUT, GPIO_PULL_UP);

hal_gpio_init_pin(GPIO_DEMO_INPUT_PIN3, GPIO_TYPE_AUTO, GPIO_DIR_INPUT, GPIO_PULL_DOWN);

hal_gpio_set_up_irq(GPIO_DEMO_INPUT_PIN0, GPIO_IRQ_EDGE, GPIO_IRQ_ACTIVE_LOW, true);

hal_gpio_set_up_irq(GPIO_DEMO_INPUT_PIN1, GPIO_IRQ_EDGE, GPIO_IRQ_ACTIVE_HIGH, true);

hal_gpio_set_up_irq(GPIO_DEMO_INPUT_PIN2, GPIO_IRQ_EDGE, GPIO_IRQ_ACTIVE_LOW, true);

hal_gpio_set_up_irq(GPIO_DEMO_INPUT_PIN3, GPIO_IRQ_EDGE, GPIO_IRQ_ACTIVE_HIGH, true);

hal_gpio_register_isr_callback(GPIO_DEMO_INPUT_PIN0, gpio_isr_cb, GPIO_DEMO_INPUT_PIN0);

hal_gpio_register_isr_callback(GPIO_DEMO_INPUT_PIN1, gpio_isr_cb, GPIO_DEMO_INPUT_PIN1);

hal_gpio_register_isr_callback(GPIO_DEMO_INPUT_PIN2, gpio_isr_cb, GPIO_DEMO_INPUT_PIN2);

hal_gpio_register_isr_callback(GPIO_DEMO_INPUT_PIN3, gpio_isr_cb, GPIO_DEMO_INPUT_PIN3);

hal_gpio_irq_enable(GPIO_DEMO_INPUT_PIN0);

hal_gpio_irq_enable(GPIO_DEMO_INPUT_PIN1);

hal_gpio_irq_enable(GPIO_DEMO_INPUT_PIN2);

hal_gpio_irq_enable(GPIO_DEMO_INPUT_PIN3);

TIMER and PWM

TIMER and PWM Demo Code Support List

Demo 1 |

tim_demo.c |

|---|---|

Sample Purpose |

Demonstrates how TIMER module works in reload mode and it will trigger the interrupt every 3 seconds. |

File Path |

|

Function Entry |

|

Timeout |

3 seconds |

Expected Result |

Print string ‘demo_hw_timer_callback’ in Debug Analyzer every 3 seconds. |

Demo 2 |

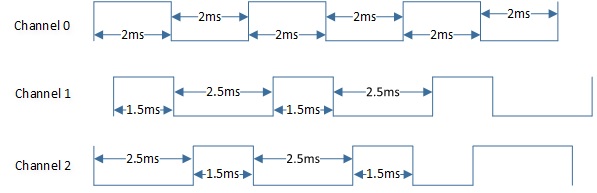

pwm_demo.c |

|---|---|

Sample Purpose |

Demonstrates PWM output, PWM complementary output, and deadzone. |

File Path |

|

Function Entry |

|

Pin Definition |

|

Hardware Connection |

Connect M0_0 of EVB to channel 0 of the logic analyzer, connect M0_2 of EVB to channel 1 of the logic analyzer, and connect M0_3 of EVB to channel 2 of the logic analyzer. |

Expected Result |

The waveforms displayed by channels 0/1/2 of the logic analyzer are shown in PWM Demo Expected Result Diagram. |

Demo 3 |

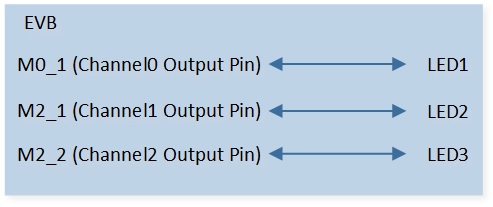

led_demo_task.c |

|---|---|

Sample Purpose |

Demonstrates how to achieve the effect of breath and blink LED with PWM. |

File Path |

|

Function Entry |

|

Pin Definition |

|

Hardware Connection |

On EVB, connect M2_1 to LED0, connect M2_2 to LED1, and connect M2_7 to LED2. |

Expected Result |

LEDs turn from dark to bright and then from bright to dark with the effect of breath light. |

Function Description

The TIMER consists of a 32-bit automatic load counter. Each TIMER is completely independent and does not share any resources. They can operate synchronously together. The TIMER can operate in two modes: user-defined count mode and free-running mode. In user-defined count mode, the TIMER counts down from the value set by the user. In free-running mode, the TIMER counts down from 0xffffffff. When the TIMER counter is enabled after being reset or disabled, the TIMER counts down from its initial value, and when it reaches 0, an interrupt is triggered.

Feature List

Two operation modes: user-defined count mode and free-running mode.

TIMER counter width: 32 bits.

Support PWM output mode.

TIMER 2 and TIMER 3 support PWM complementary output mode.

TIMER 2 and TIMER 3 support deadzone.

TIMER 2 and TIMER 3 support emergency stop control.

Note

RTL87x3D supports up to 16 TIMER, 12 of which can be used for application.

RTL87x3E supports up to 8 TIMER, 5 of which can be used for application.

RTL87x3EP supports up to 12 TIMER, 9 of which can be used for application, but only 5 of which can be used for the PWM function.

TIMER 0 and TIMER 1 are reserved for low stack. TIMER 7 is reserved for log time stamp.

TIMER Operation Flow

The codes below demonstrate the TIMER operation flow. For details, please refer to src\sample\io_demo\tim\interrupt\tim_demo.c.

void tim_driver_init(void)

{

/* Create the timer, user-defined mode, the period is 3 seconds. */

demo_timer_handle = hw_timer_create("demo_hw_timer", 3000 * 1000, true, demo_hw_timer_callback);

if (demo_timer_handle == NULL)

{

IO_PRINT_ERROR0("tim_driver_init: fail to create hw timer, check hw timer usage");

return;

}

IO_PRINT_TRACE1("tim_driver_init: create hw timer instance successfully, id %d",

hw_timer_get_id(demo_timer_handle));

/* Start the specified timer */

hw_timer_start(demo_timer_handle);

}

When the TIMER counter reaches to zero, the interrupt will be triggered and the callback will be executed. The codes below demonstrate the TIMER callback handle flow.

void demo_hw_timer_callback(T_HW_TIMER_HANDLE handle)

{

//Add User code here

IO_PRINT_TRACE0("demo_hw_timer_callback");

}

PWM Operation Flow

The codes below demonstrate the PWM operation flow. For details, please refer to src\sample\io_demo\tim\pwm\pwm_demo.c.

static void driver_pwm_init(void)

{

T_PWM_CONFIG demo_pwm_deadzone_para;

/* Create the PWM, high-level time is 2 seconds, low-level time is 2 seconds */

demo_pwm_handle = pwm_create("demo_pwm", PWM_HIGH_LEVEL_CNT, PWM_LOW_LEVEL_CNT, false);

if (demo_pwm_handle == NULL)

{

IO_PRINT_ERROR0("driver_pwm_init: Fail to create pwm handle");

return;

}

/* Configure PIN ADC_0 as PWM output */

pwm_pin_config(demo_pwm_handle, PWM_OUT_PIN, PWM_FUNC);

/* Start the specified PWM */

pwm_start(demo_pwm_handle);

/* Create the PWM, deadzone is enabled. */

demo_pwm_deadzone_handle = pwm_create("demo_pwm_deadzone", PWM_HIGH_LEVEL_CNT, PWM_LOW_LEVEL_CNT,

true);

if (demo_pwm_deadzone_handle == NULL)

{

IO_PRINT_ERROR0("driver_pwm_init: Fail to create pwm deadzone handle");

return;

}

/* Set high-level time */

demo_pwm_deadzone_para.pwm_high_count = PWM_HIGH_LEVEL_CNT;

/* Set low-level time */

demo_pwm_deadzone_para.pwm_low_count = PWM_LOW_LEVEL_CNT;

/* Enable deadzone */

demo_pwm_deadzone_para.pwm_deadzone_enable = ENABLE;

/* Configure PWM clock source as 1MHz */

demo_pwm_deadzone_para.clock_source = PWM_CLOCK_1M;

/* Set deadzone size count, count frequency is 32K */

demo_pwm_deadzone_para.pwm_deadzone_size = PWM_DEADZONE_SIZE_CNT;

/* Configure PWM_P emergency stop state as low-level */

demo_pwm_deadzone_para.pwm_p_stop_state = PWM_DEAD_ZONE_STOP_LOW;

/* Configure PWM_N emergency stop state as high-level */

demo_pwm_deadzone_para.pwm_n_stop_state = PWM_DEAD_ZONE_STOP_HIGH;

/* Initialize PWM */

pwm_config(demo_pwm_deadzone_handle, &demo_pwm_deadzone_para);

/* Configure PIN ADC_2 as PWM_P output */

pwm_pin_config(demo_pwm_deadzone_handle, PWM_OUT_PIN_P, PWM_FUNC_P);

/* Configure PIN ADC_3 as PWM_N output */

pwm_pin_config(demo_pwm_deadzone_handle, PWM_OUT_PIN_N, PWM_FUNC_N);

/* Start the specified PWM */

pwm_start(demo_pwm_deadzone_handle);

}

UART

UART Demo Code Support List

Demo 1 |

uart_polling_demo.c |

|---|---|

Sample Purpose |

Demonstrate how UART sends and receives data in polling mode. |

Brief Introduction |

This sample code demonstrates the communication between chip and PC. PC transmits some data to chip and then chip returns the same data received to PC. |

File Path |

|

Function Entry |

|

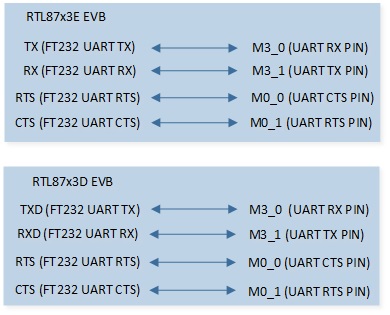

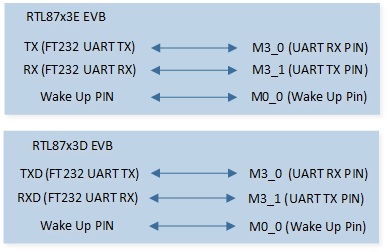

Hardware Connection |

As shown in UART Demo 1/2/3/5 Hardware Connection Diagram. |

UART TX Pin Definition |

|

UART RX Pin Definition |

|

UART ID |

UART0 |

Baud Rate |

115200 |

Parity Check |

No Parity |

Data Format |

8-Bit |

Stop Bit |

1-Bit |

Hardware Flow Control |

None |

Expected Result |

1. Press the reset button on the EVB, string ‘### Welcome to use RealTek Bumblebee ###\r\n’ will be displayed in UART debug tool. |

Demo 2 |

uart_demo.c |

|---|---|

Sample Purpose |

Demonstrate how UART receives data in interrupt mode. |

Brief Introduction |

This sample code demonstrates the communication between chip and PC. PC transmits some data to chip and then chip returns the same data received to PC. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in UART Demo 1/2/3/5 Hardware Connection Diagram. |

UART TX Pin Definition |

|

UART RX Pin Definition |

|

UART ID |

UART0 |

Baud Rate |

115200 |

Parity Check |

No Parity |

Data Format |

8-Bit |

Stop Bit |

1-Bit |

Hardware Flow Control |

None |

Expected Result |

1. Press the reset button on the EVB, string ‘### Welcome to use RealTek Bumblebee ###\r\n’ will be displayed in UART debug tool. |

Demo 3 |

uart_tx_demo.c |

|---|---|

Sample Purpose |

Demonstrate how UART sends data in interrupt mode. |

Brief Introduction |

This sample code demonstrates the communication between chip and PC. Chip transmits some data to PC. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in UART Demo 1/2/3/5 Hardware Connection Diagram. |

UART TX Pin Definition |

|

UART RX Pin Definition |

|

UART ID |

UART0 |

Baud Rate |

115200 |

Parity Check |

No Parity |

Data Format |

8-Bit |

Stop Bit |

1-Bit |

Hardware Flow Control |

None |

Expected Result |

Press the reset button on the EVB, string ‘### Welcome to use RealTek Bumblebee ###\r\n’ will be displayed in UART debug tool. |

Demo 4 |

uart_fc_demo.c |

|---|---|

Sample Purpose |

Demonstrate how UART sends and receives data with hardware flow control. |

Brief Introduction |

This sample code demonstrates the communication between chip and PC. PC transmits some data to chip and then chip returns the same data received to PC. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in UART Demo 4 Hardware Connection Diagram. |

UART TX Pin Definition |

|

UART RX Pin Definition |

|

UART CTS Pin Definition |

|

UART RTS Pin Definition |

|

UART ID |

UART0 |

Baud Rate |

115200 |

Parity Check |

No Parity |

Data Format |

8-Bit |

Stop Bit |

1-Bit |

Hardware Flow Control |

CTS and RTS Flow Control. |

Expected Result |

1. Press the reset button on the EVB, string ‘### Uart demo–Auto Hardware Flow Contrl ###\r\n’ will be displayed in UART debug tool. |

Demo 5 |

dlps_uart_demo.c |

|---|---|

Sample Purpose |

Demonstrates how UART wakes up the system from DLPS mode. |

Brief Introduction |

This sample code demonstrates the communication between chip and PC. It realizes the function that transmits and receives data through UART and wakes up the system by UART after entering DLPS mode. System will enter DLPS mode automatically while it is in idle state. When some data is sent to chip, |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in UART Demo 1/2/3/5 Hardware Connection Diagram. |

UART TX Pin Definition |

|

UART RX Pin Definition |

|

UART ID |

UART2 |

Baud Rate |

115200 |

Parity Check |

No Parity |

Data Format |

8-Bit |

Stop Bit |

1-Bit |

Hardware Flow Control |

None |

Expected Result |

1. Press the reset button on the EVB, string ‘### Welcome to use RealTek Bumblebee ###\r\n’ will be displayed in UART debug tool. |

Demo 6 |

adp_1wire_uart_demo.c |

|---|---|

Sample Purpose |

Demonstrates how adapter one-wire works. |

Brief Introduction |

This sample code demonstrates how adapter one-wire works. When the adapter plugs in, it works as UART RX. When the adapter plugs out, it works as GPIO. |

File Path |

|

Function Entry |

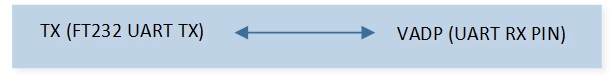

|

Hardware Connection |

As shown in UART Demo 6 Hardware Connection Diagram. On EVB, TX of FT232 is connected to VADP. |

UART RX Pin Definition |

RTL87x3D: |

UART ID |

UART0 |

Baud Rate |

9600 |

Parity Check |

No Parity |

Data Format |

8-Bit |

Stop Bit |

1-Bit |

Hardware Flow Control |

None |

Expected Result |

1. Press the reset button on the EVB. |

Function Description

UART provides a flexible method for full-duplex data exchange with external devices. The UART utilizes a fractional baud rate generator to provide a wide range of baud rate options. It supports half-duplex single-wire communication. UART can also be used with GDMA to achieve high-speed data communication..

Feature List

Support 1-bit or 2-bit stop bit.

Support 7-bit or 8-bit data format.

Support odd or even parity.

Support hardware flow control.

Programmable baud rate.

Support GDMA.

Support one-wire UART.

Note

RTL87x3D supports 4 UART. RTL87x3E and RTL87x3EP support 3 UART. UART1 is used as log UART.

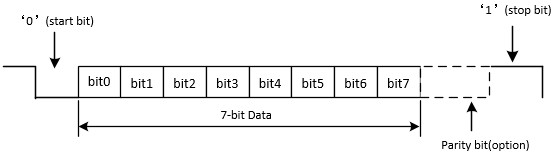

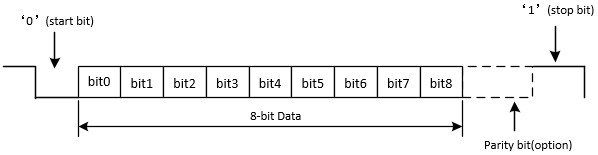

Data Format

The schematic diagram of the 7-bit data format is shown in the following figure.

The schematic diagram of the 8-bit data format is shown in the following figure.

Parity Check

Odd Parity

Odd parity means that the number of ‘1’ in the data bits and check bit is odd. When the number of ‘1’ in the data bits is odd, the check bit is ‘0’; otherwise, it is ‘1’.

Even Parity

Even parity means that the number of ‘1’ in the data bits and check bit is even. When the number of ‘1’ in the data bits is even, the check bit is ‘0’; otherwise, it is ‘1’.

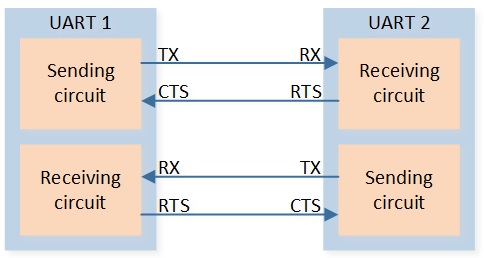

Hardware Flow Control

The schematic diagram of hardware flow control is shown in the following figure.

RTS Flow Control

When the UART receiver is ready to accept new data, RTS becomes valid, and the low level is valid. When the number of data in the RX FIFO reaches the set RX trigger level, RTS becomes invalid (high level is invalid), thereby indicating that it is desired to stop data transmission at the end of the current frame.

CTS Flow Control

The transmitter checks the CTS before sending the next frame. If CTS is valid (low level is valid), the next data is sent; otherwise, the next frame data is not sent. If the CTS becomes invalid (high level is invalid) during transmission, the transmission is stopped after the current transmission is completed.

Baud Rate

Set the baud rate by configuring the variables div, ovsr, and ovsr_adj. UART baud rate table is shown below.

Baud Rate |

Variable div |

Variable ovsr |

Variable ovsr_adj |

|---|---|---|---|

1200 |

2589 |

7 |

0x7F7 |

9600 |

271 |

10 |

0x24A |

14400 |

271 |

5 |

0x222 |

19200 |

123 |

11 |

0x6FF |

28800 |

82 |

11 |

0x6FF |

38400 |

85 |

7 |

0x222 |

57600 |

41 |

11 |

0x6FF |

76800 |

35 |

9 |

0x7EF |

115200 |

20 |

12 |

0x252 |

128000 |

25 |

7 |

0x555 |

153600 |

15 |

12 |

0x252 |

230400 |

10 |

12 |

0x252 |

460800 |

5 |

12 |

0x252 |

500000 |

8 |

5 |

0 |

921600 |

3 |

9 |

0x2AA |

1000000 |

4 |

5 |

0 |

1382400 |

2 |

9 |

0x2AA |

1444400 |

2 |

8 |

0x5F7 |

1500000 |

2 |

8 |

0x492 |

1843200 |

2 |

5 |

0x3F7 |

2000000 |

2 |

5 |

0 |

2100000 |

2 |

14 |

0x400 |

2764800 |

1 |

9 |

0x2AA |

3000000 |

1 |

8 |

0x492 |

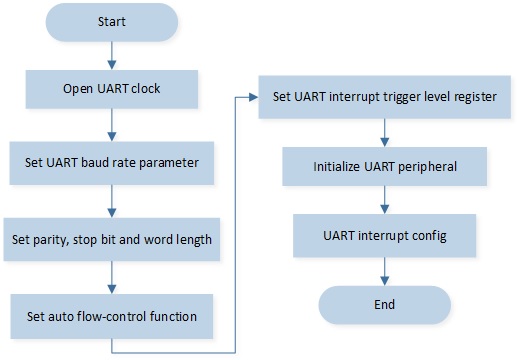

Initialization Flow

UART initialization flow is shown in the following figure.

The codes below demonstrate the UART interrupt handle flow.

/* Enable UART0 clock */

RCC_PeriphClockCmd(APBPeriph_UART0, APBPeriph_UART0_CLOCK, ENABLE);

UART_InitTypeDef uartInitStruct;

/* Fill each UART_InitTypeDef member variable with its default value */

UART_StructInit(&uartInitStruct);

/* Change default rx trigger level */

uartInitStruct.rxTriggerLevel = UART_RX_FIFO_TRIGGER_LEVEL_14BYTE;

UART_Init(UART0, &uartInitStruct);

//enable rx interrupt and line status interrupt

UART_INTConfig(UART0, UART_INT_RD_AVA | UART_INT_LINE_STS | UART_INT_IDLE, ENABLE);

RamVectorTableUpdate(UART0_VECTORn, (IRQ_Fun)Data_Uart_Handler);

NVIC_InitTypeDef NVIC_InitStruct;

NVIC_InitStruct.NVIC_IRQChannel = UART0_IRQn;

NVIC_InitStruct.NVIC_IRQChannelPriority = 3;

NVIC_InitStruct.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStruct);

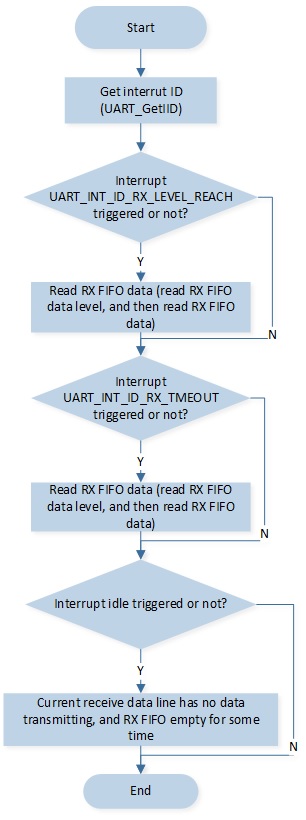

Receive Data by Interrupt Mode

UART interrupt handle flow is shown in the following figure.

The codes below demonstrate the UART interrupt handle flow.

void data_uart_handler(void)

{

uint8_t event = IO_DEMO_EVENT_UART_RX;

uint32_t int_status = 0;

uint8_t recv_len;

uint8_t line_status = 0;

if (UART_GetFlagState(UART0, UART_FLAG_RX_IDLE) == SET)

{

UART_INTConfig(UART0, UART_INT_IDLE, DISABLE);

if (os_msg_send(io_queue_handle, &event, 0) == false)

{

IO_PRINT_ERROR0("data_uart_handler: Send Queue Error");

}

//user code here

UART_INTConfig(UART0, UART_INT_IDLE, ENABLE);

}

/* read interrupt id */

int_status = UART_GetIID(UART0);

switch (int_status)

{

/* tx fifo empty, not enable */

case UART_INT_ID_TX_EMPTY:

break;

/* rx data available */

case UART_INT_ID_RX_LEVEL_REACH:

recv_len = UART_GetRxFIFOLen(UART0);

UART_ReceiveData(UART0, &RxBuffer[RxCount], recv_len);

RxCount += recv_len;

break;

case UART_INT_ID_RX_TMEOUT:

recv_len = UART_GetRxFIFOLen(UART0);

UART_ReceiveData(UART0, &RxBuffer[RxCount], recv_len);

RxCount += recv_len;

break;

/* receive line status interrupt */

case UART_INT_ID_LINE_STATUS:

line_status = UART_GetLineStatus(UART0);

IO_PRINT_ERROR1("data_uart_handler: line_status 0x%x", line_status);

UART_SendByte(UART0, line_status);

break;

default:

break;

}

return;

}

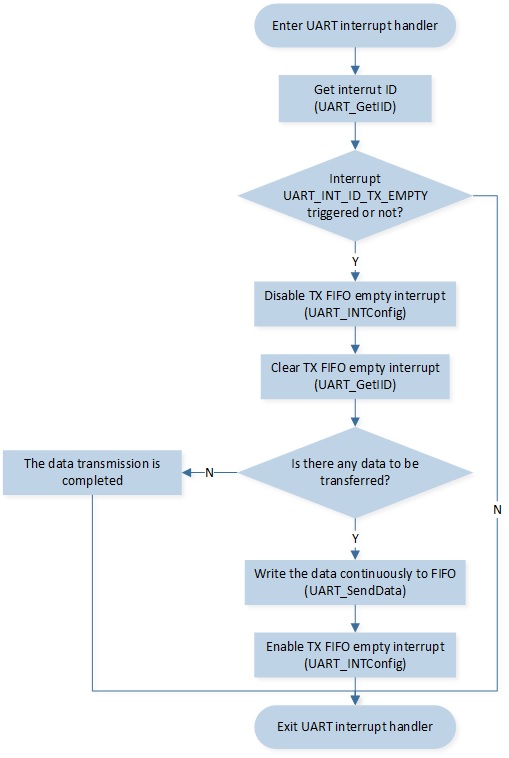

Send Data

UART interrupt handle flow is shown in the following figure.

The codes below demonstrate the UART interrupt handle flow.

static void uart_send_data(uint8_t *buf, uint32_t len)

{

uint32_t tx_len = len > UART_TX_FIFO_SIZE ? UART_TX_FIFO_SIZE : len;

UART_SendData(UART0, buf, tx_len);

uart_tx_curr_addr = buf + tx_len;

uart_tx_len = len - tx_len;

UART_INTConfig(UART0, UART_INT_FIFO_EMPTY, ENABLE);

}

static void uart0_interrupt_handler(void)

{

uint32_t int_status = 0;

/* read interrupt id */

int_status = UART_GetIID(UART0);

switch (int_status)

{

/* tx fifo empty */

case UART_INT_ID_TX_EMPTY:

UART_INTConfig(UART0, UART_INT_FIFO_EMPTY, DISABLE);

UART_GetIID(UART0);

if (uart_tx_len)

{

uart_send_data(uart_tx_curr_addr, uart_tx_len);

}

break;

/* rx data available */

case UART_INT_ID_RX_LEVEL_REACH:

break;

case UART_INT_ID_RX_TMEOUT:

break;

/* receive line status interrupt */

case UART_INT_ID_LINE_STATUS:

break;

default:

break;

}

return;

}

GDMA

GDMA Demo Code Support List

Demo 1 |

gdma_demo.c |

|---|---|

Sample Purpose |

Demonstrate memory to memory by GDMA. |

Brief Introduction |

This sample code demonstrates memory to memory by GDMA. The data in |

File Path |

|

Function Entry |

|

GDMA DIR |

|

GDMA BufferSize |

100 |

GDMA SourceInc |

|

GDMA DestinationInc |

|

GDMA SourceDataSize |

|

GDMA DestinationDataSize |

|

GDMA SourceMsize |

|

GDMA DestinationMsize |

|

GDMA SourceAddr |

|

GDMA DestinationAddr |

|

Expected Result |

1. Press the reset button on the EVB. |

Demo 2 |

dma_multiblock_demo.c |

|---|---|

Sample Purpose |

Demonstrate how GDMA multi-block function works. |

Brief Introduction |

This sample code demonstrates how GDMA multi-block function works. The data in |

File Path |

|

Function Entry |

|

GDMA DIR |

|

GDMA BufferSize |

100 |

GDMA SourceInc |

|

GDMA DestinationInc |

|

GDMA SourceDataSize |

|

GDMA DestinationDataSize |

|

GDMA SourceMsize |

|

GDMA DestinationMsize |

|

GDMA SourceAddr |

|

GDMA DestinationAddr |

|

GDMA Multi-Block Mode |

|

Expected Result |

1. Press the reset button on the EVB. |

Demo 3 |

dma_scrgar_demo.c |

|---|---|

Sample Purpose |

Demonstrate memory to memory transfer by scatter/gather GDMA. |

Brief Introduction |

This sample code demonstrates how GDMA scatter/gather function works. The data in |

File Path |

|

Function Entry |

|

GDMA DIR |

|

GDMA BufferSize |

20 |

GDMA SourceInc |

|

GDMA DestinationInc |

|

GDMA SourceDataSize |

|

GDMA DestinationDataSize |

|

GDMA SourceMsize |

|

GDMA DestinationMsize |

|

GDMA SourceAddr |

|

GDMA DestinationAddr |

|

GDMA Scatter Mode |

|

GDMA Scatter Count |

4 |

GDMA Scatter Interval |

4 |

Expected Result |

1. Press the reset button on the EVB. |

Demo 4 |

uart_rx_dma.c |

|---|---|

Sample Purpose |

Demonstrate how UART receives data by GDMA. |

Brief Introduction |

This sample code demonstrates the communication between chip and PC. PC transmits some data to chip. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in UART Demo 1/2/3/5 Hardware Connection Diagram. |

UART TX Pin Definition |

|

UART RX Pin Definition |

|

UART ID |

UART0 |

Baud Rate |

3000000 |

Parity Check |

No Parity |

Data Format |

8-Bit |

Stop Bit |

1-Bit |

Hardware Flow Control |

None |

Expected Result |

1. Press the reset button on the EVB, string ‘### Welcome to use RealTek Bumblebee ###\r\n’ will be displayed in UART debug tool. |

Demo 5 |

uart_tx_gdma.c |

|---|---|

Sample Purpose |

Demonstrate how UART sends data by GDMA. |

Brief Introduction |

This sample code demonstrates the communication between chip and PC. Chip transmits some data to PC. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in UART Demo 1/2/3/5 Hardware Connection Diagram. |

UART TX Pin Definition |

|

UART RX Pin Definition |

|

UART ID |

UART0 |

Baud Rate |

115200 |

Parity Check |

No Parity |

Data Format |

8-Bit |

Stop Bit |

1-Bit |

Hardware Flow Control |

None |

Expected Result |

Press the reset button on the EVB, string ‘### Welcome to use RealTek Bumblebee ###\r\n’ will be displayed in UART debug tool. |

Demo 6 |

adc_gdma_demo.c |

|---|---|

Sample Purpose |

Demonstrate how ADC samples data in continuous mode by GDMA. |

Brief Introduction |

Use continuous mode of ADC peripheral to measure voltage on P0_0 and P0_1. |

File Path |

|

Function Entry |

|

Pre-Condition |

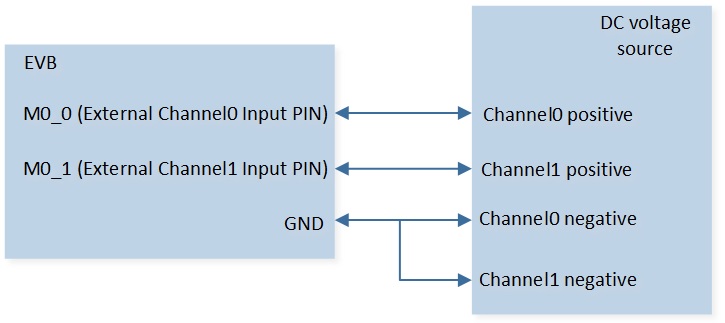

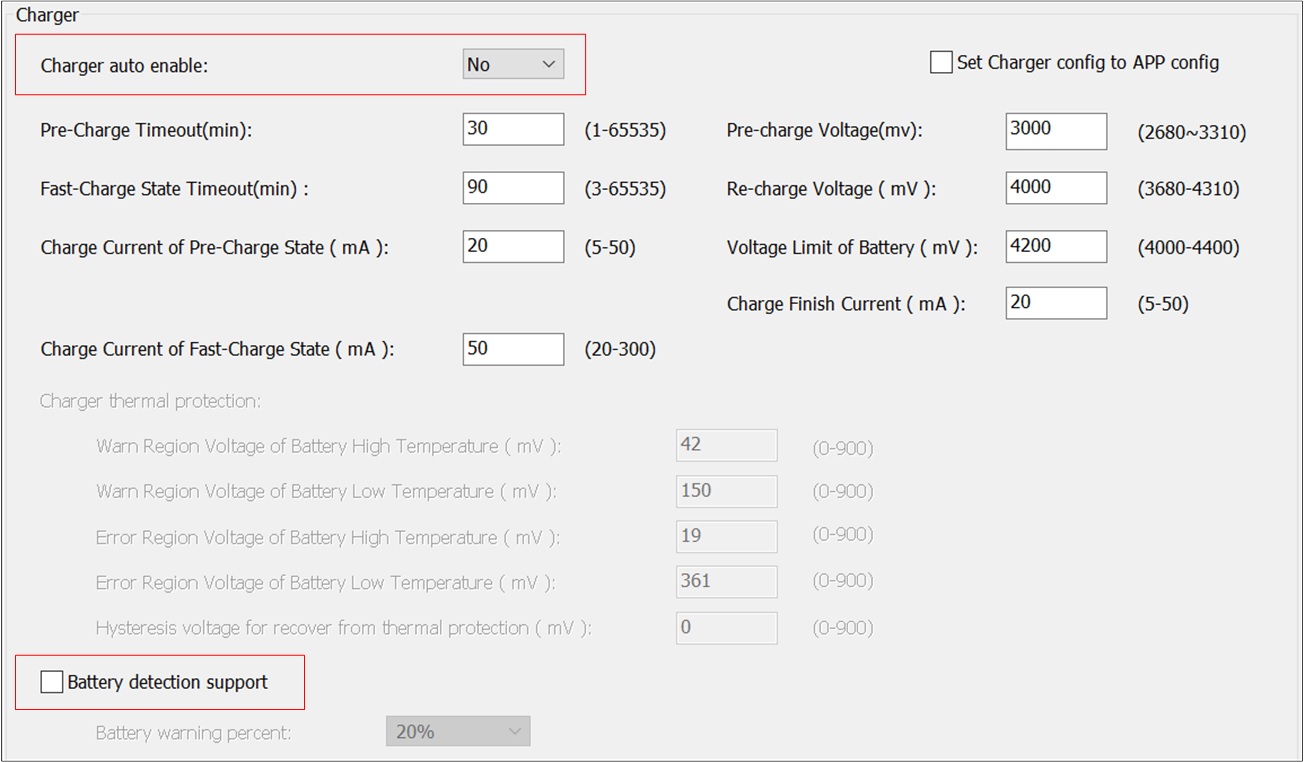

Turn off ‘Charger auto enable’ and ‘Battery detection support’ on the MCUConfig Tool. |

Channel |

ADC0 |

External Channel Input Mode |

ADC0 and ADC1 are divide mode. |

Hardware Connection |

Connect M0_0 and M0_1 of EVB to external DC voltage source. Input voltage of M0_0 and M0_1 must range from 0 to 3.3V. |

Expected Result |

Press the reset button on the EVB, ADC starts continuous sampling, and sample rawdata will be stored in array |

Demo 7 |

i2c_dma_demo.c |

|---|---|

Sample Purpose |

Demonstrate how I2C master and slave work in GDMA mode. |

Brief Introduction |

This sample code demonstrates the communication between I2C master and slave in GDMA mode. Master will read data from slave. |

File Path |

|

Function Entry |

|

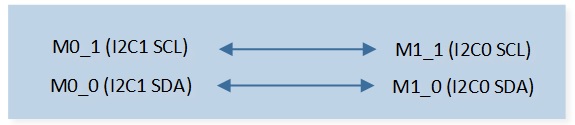

Hardware Connection |

As shown in I2C GDMA Hardware Connection Diagram. On EVB, connect P0_0 to P1_0, connect P0_1 to P1_1. |

I2C Master SCL Pin Definition |

|

I2C Master SDA Pin Definition |

|

I2C Slave SCL Pin Definition |

|

I2C Slave SDA Pin Definition |

|

I2C Master ID |

I2C1 |

I2C Slave ID |

I2C0 |

Clock Speed |

400000 |

Address Mode |

7-Bit |

Slave Address |

0x50 |

ACK |

ACK Enable |

GDMA DIR |

Master: |

GDMA BufferSize |

|

GDMA SourceInc |

Master: |

GDMA DestinationInc |

Master: |

GDMA SourceDataSize |

Master: |

GDMA DestinationDataSize |

Master: |

GDMA SourceMsize |

|

GDMA DestinationMsize |

|

GDMA SourceAddr |

Master: |

GDMA DestinationAddr |

Master: |

GDMA SourceHandshake |

Master: |

GDMA DestHandshake |

Slave: |

Expected Result |

1. Press the reset button on the EVB. |

Demo 8 |

dlps_gdma_recover_demo.c |

|---|---|

Sample Purpose |

Demonstrate how GDMA recovers from DLPS. |

Brief Introduction |

This sample code demonstrates how GDMA recovers from DLPS. The UART can receive data through GDMA when the chip wakes up from DLPS. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in GDMA Recover From DLPS Hardware Connection Diagram. |

UART TX Pin Definition |

|

UART RX Pin Definition |

|

UART ID |

UART0 |

Baud Rate |

3000000 |

Parity Check |

No Parity |

Data Format |

8-Bit |

Stop Bit |

1-Bit |

Hardware Flow Control |

None |

Expected Result |

1. Press the reset button on the EVB, string ‘### Welcome to use RealTek Bumblebee ###\r\n’ will be displayed in UART debug tool. |

Demo 9 |

spi_dma_demo.c |

|---|---|

Sample Purpose |

Demonstrate how SPI sends and receives data in master mode by GDMA. |

File Path |

|

Function Entry |

|

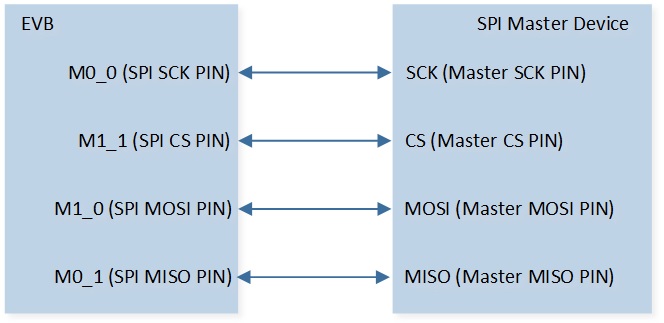

Hardware Connection |

As shown in SPI Demo 4 Hardware Connection Diagram. Connect M0_1 to CS of SPI slave device, connect M0_0 to SCK of SPI slave device, connect M1_0 to MISO of SPI slave device, and connect M1_1 to MOSI of SPI slave device. |

SPI CS Pin Definition |

|

SPI SCK Pin Definition |

|

SPI MOSI Pin Definition |

|

SPI MISO Pin Definition |

|

SPI ID |

SPI1 |

Mode |

Master |

Speed |

400000 |

Data Size |

8-Bit |

Expected Result |

1. Press the reset button on the EVB, the data in array sendbuf is sent to SPI slave device and prints the string ‘spi_tx_dma_handler’ in the Debug Analyzer. |

Function Description

GDMA is used to provide high-speed data transfer between peripherals and memory or between memory and memory. The data transfer can be done independently of the CPU to reduce the CPU overhead.

Each channel of the GDMA controller can handle requests from one or more peripherals for memory access. The GDMA controller has an arbitrator to coordinate the priority of each GDMA request.

Feature List

Programmable transfer type for each channel: memory to memory, memory to peripheral, peripheral to memory, peripheral to peripheral.

Programmable source and destination addresses for each channel.

Address increment, or fixed.

Programmable burst transaction size for each channel.

Support transfer abort/suspend function.

Programmable channel priority.

Independent interrupts and control bit for every channel.

Support single-block and multi-block transfer.

Support scatter and gather transfer.

Note

RTL87x3D supports 16 channels, if using SPI high-speed mode, please use channel 0 and 1. RTL87x3E supports 9 channels, RTL87x3EP supports 12 channels.

Parameter Significance

GDMA_ChannelNumChannel numbers can be 0 to 15.

GDMA_DIRThe transfer direction can be memory to memory or memory to peripheral or peripheral to memory or peripheral to peripheral.

GDMA_SourceIncIndicates whether to increment the source address on every source transfer.

GDMA_DestinationIncIndicates whether to increment the destination address on every destination transfer.

GDMA_SourceDataSizeSource single transaction size in bytes:

src_single_size_bytes =

GDMA_SourceDataSizeGDMA_DestinationDataSizeDestination single transaction size in bytes:

dst_single_size_bytes =

GDMA_DestinationDataSizeGDMA_SourceMsizeSource burst transaction size in bytes:

src_burst_size_bytes =

GDMA_SourceMsize* src_single_size_bytesGDMA_DestinationMsizeDestination burst transaction size in bytes:

dst_burst_size_bytes =

GDMA_DestinationMsize* dst_single_size_bytesGDMA_BufferSizeThe total number of bytes to be transferred in a block is:

blk_size_bytes_dma =

GDMA_BufferSize* src_single_size_bytes

Note

The above parameter configuration needs to satisfy the following formula:

GDMA_SourceDataSize * GDMA_SourceMsize = GDMA_DestinationDataSize * GDMA_DestinationMsize

Waterlevel Setting

Handshaking interfaces are used at the transaction level to control the flow of single or burst transactions. Waterlevel is mainly divided into TX FIFO waterlevel and RX FIFO waterlevel. When the effective data amount in the FIFO reaches the set value of waterlevel, a burst transmission is initiated. GDMA_SourceMsize, GDMA_DestinationMsize, GDMA_SourceDataSize, GDMA_DestinationDataSize and peripheral waterlevel setting table is presented below.

IO |

Dir |

Peripheral |

GDMA_ |

GDMA_ |

GDMA_ |

GDMA_ |

|---|---|---|---|---|---|---|

UART |

TX |

.TxWaterlevel |

1 |

4 |

Word |

Byte |

RX |

.RxWaterlevel |

4 |

1 |

Byte |

Word |

|

SPI |

TX |

.SPI_TxWaterlevel |

4 |

8 |

Word |

HalfWord |

RX |

.SPI_RxWaterlevel |

8 |

4 |

HalfWord |

Word |

|

TX |

.SPI_TxWaterlevel |

1 |

4 |

Word |

Byte |

|

RX |

.SPI_RxWaterlevel |

4 |

1 |

Byte |

Word |

|

SPI |

TX |

.SPI_TxWaterlevel |

1 |

4 |

Word |

Byte |

RX |

.SPI_RxWaterlevel |

4 |

1 |

Byte |

Word |

|

I2C |

TX |

.I2C_TxWaterlevel |

4 |

8 |

Word |

HalfWord |

RX |

.I2C_RxWaterlevel |

4 |

1 |

Byte |

Word |

|

ADC |

.adcBurstSize |

8 |

8 |

HalfWord |

HalfWord |

|

SPI_HS |

TX |

.SPI_TxWaterlevel |

32 |

32 |

Byte |

Byte |

RX |

.SPI_RxWaterlevel |

32 |

32 |

Byte |

Byte |

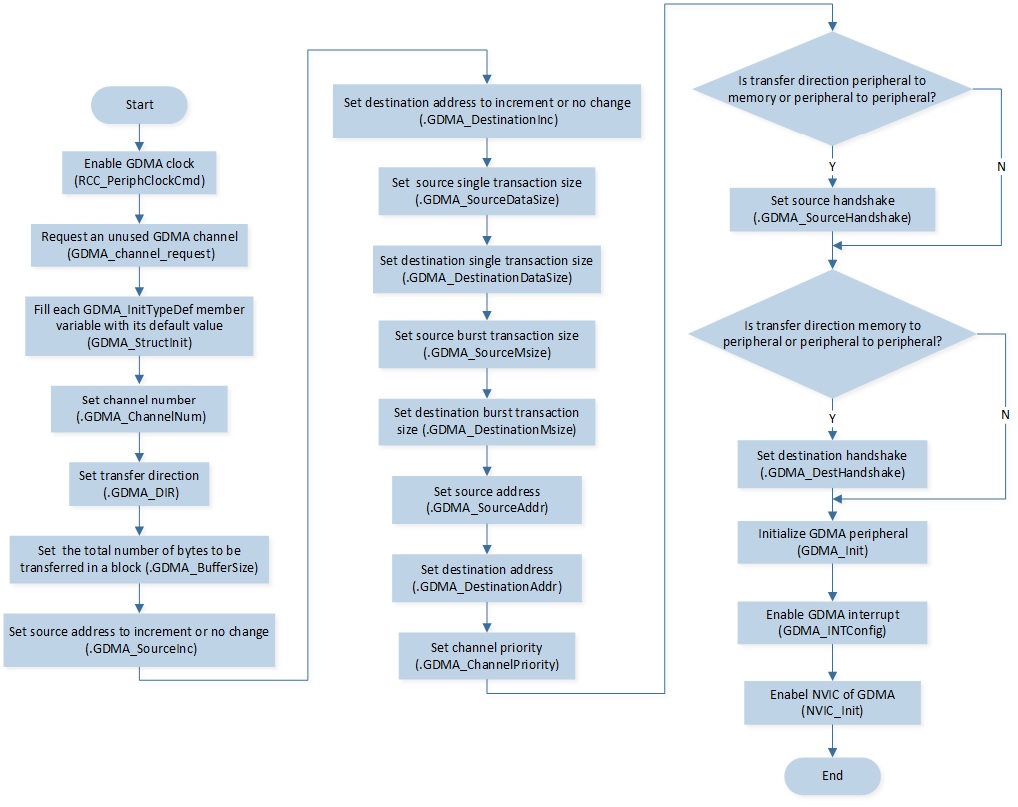

GDMA Single-Block Transfer Initialization Flow

The initialization flow of GDMA single-block transfer is shown in the following figure.

The codes below demonstrate the GDMA single-block transfer.

uint16_t i = 0;

RCC_PeriphClockCmd(APBPeriph_GDMA, APBPeriph_GDMA_CLOCK, ENABLE);

GDMA_InitTypeDef GDMA_InitStruct;

if (!GDMA_channel_request(&mem_to_mem_dma_ch_num, demo_dma_handler, true))

{

return;

}

/*--------------initialize test buffer---------------------*/

for (i = 0; i < 100; i++)

{

GDMA_SendBuffer[i] = (i & 0xff);

}

for (i = 0; i < 100; i++)

{

GDMA_RecvBuffer[i] = 0;

}

GDMA_StructInit(&GDMA_InitStruct);

GDMA_InitStruct.GDMA_ChannelNum = DEMO_DMA_CHANNEL_NUM;

GDMA_InitStruct.GDMA_DIR = GDMA_DIR_MemoryToMemory;

GDMA_InitStruct.GDMA_BufferSize = 100;//determine total transfer size

GDMA_InitStruct.GDMA_SourceInc = DMA_SourceInc_Inc;

GDMA_InitStruct.GDMA_DestinationInc = DMA_DestinationInc_Inc;

GDMA_InitStruct.GDMA_SourceDataSize = GDMA_DataSize_Byte;

GDMA_InitStruct.GDMA_DestinationDataSize = GDMA_DataSize_Byte;

GDMA_InitStruct.GDMA_SourceMsize = GDMA_Msize_1;

GDMA_InitStruct.GDMA_DestinationMsize = GDMA_Msize_1;

GDMA_InitStruct.GDMA_SourceAddr = (uint32_t)GDMA_SendBuffer;

GDMA_InitStruct.GDMA_DestinationAddr = (uint32_t)GDMA_RecvBuffer;

GDMA_Init(DEMO_DMA_CHANNEL, &GDMA_InitStruct);

/*-----------------GDMA IRQ init-------------------*/

NVIC_InitTypeDef nvic_init_struct;

nvic_init_struct.NVIC_IRQChannel = DEMO_DMA_IRQ;

nvic_init_struct.NVIC_IRQChannelCmd = (FunctionalState)ENABLE;

nvic_init_struct.NVIC_IRQChannelPriority = 3;

NVIC_Init(&nvic_init_struct);

GDMA_INTConfig(DEMO_DMA_CHANNEL_NUM, GDMA_INT_Block, ENABLE);

GDMA_Cmd(DEMO_DMA_CHANNEL_NUM, ENABLE);

I2C

I2C Demo Code Support List

Demo 1 |

i2c_demo.c |

|---|---|

Sample Purpose |

Demonstrate how I2C writes and reads data in interrupt mode. |

Brief Introduction |

This sample code demonstrates the communication between the chip and I2C slave. The chip writes some data to I2C slave and then chip reads data from I2C slave. |

File Path |

|

Function Entry |

|

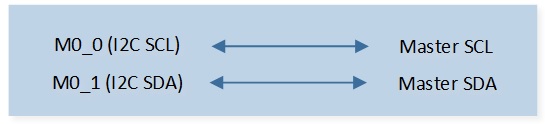

Hardware Connection |

As shown in I2C Demo 1/2/3 Hardware Connection Diagram. On EVB, connect P0_0 to the SCL of the I2C slave, connect P0_1 to the SDA of the I2C slave. |

I2C SCL Pin Definition |

|

I2C SDA Pin Definition |

|

I2C ID |

I2C0 |

Clock Speed |

100000 |

Device Mode |

Master |

Address Mode |

7 Bit |

Slave Address |

0x50 |

ACK |

ACK Enable |

Expected Result |

1. Press the reset button on the EVB, the I2C slave will receive data 0xaa and 0xbb, and the chip will receive four bytes from the I2C slave. |

Demo 2 |

i2c_mw_demo.c |

|---|---|

Sample Purpose |

Demonstrate I2C master write function. |

Brief Introduction |

This sample code demonstrates the I2C master write function. The chip transmits some data to the I2C slave. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in I2C Demo 1/2/3 Hardware Connection Diagram. On EVB, connect P0_0 to the SCL of the I2C slave, connect P0_1 to the SDA of the I2C slave. |

I2C SCL Pin Definition |

|

I2C SDA Pin Definition |

|

I2C ID |

I2C1 |

Clock Speed |

400000 |

Device Mode |

Master |

Address Mode |

7 Bit |

Slave Address |

|

ACK |

ACK Enable |

Expected Result |

1. Press the reset button on the EVB, the I2C slave will receive data 0xaa, 0xbb, 0x66, 0x68, 0x77, 0x88. |

Demo 3 |

i2c_polling_demo.c |

|---|---|

Sample Purpose |

Demonstrate how I2C writes and reads data in polling mode. |

Brief Introduction |

This sample code demonstrates the communication between the chip and the I2C slave. The chip writes some data to the I2C slave and then the chip reads data from the I2C slave. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in I2C Demo 1/2/3 Hardware Connection Diagram. On EVB, connect P0_0 to the SCL of the I2C slave, connect P0_1 to the SDA of the I2C slave. |

I2C SCL Pin Definition |

|

I2C SDA Pin Definition |

|

I2C ID |

I2C1 |

Clock Speed |

400000 |

Device Mode |

Master |

Address Mode |

7 Bit |

Slave Address |

|

ACK |

ACK Enable |

Expected Result |

1. Press the reset button on the EVB, the I2C slave will receive data 0xaa and 0xbb, and the chip will receive four bytes from the I2C slave. |

Demo 4 |

i2c_slave_demo.c |

|---|---|

Sample Purpose |

Demonstrate how I2C slave works. |

Brief Introduction |

This sample code demonstrates the communication between the chip and I2C master. The chip can read data from the I2C master and write data to the I2C master. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in I2C Demo 4 Hardware Connection Diagram. On EVB, connect P0_0 to the SCL of the I2C master. On EVB, connect P0_1 to the SDA of the I2C master. |

I2C SCL Pin Definition |

|

I2C SDA Pin Definition |

|

I2C ID |

I2C1 |

Clock Speed |

100000 |

Device Mode |

Slave |

Address Mode |

7 Bit |

Slave Address |

0x50 |

ACK |

ACK Enable |

Expected Result |

1. Press the reset button on the EVB. |

Function Description

The I2C bus is a two-wire serial interface, consisting of a serial data line (SDA) and a serial clock (SCL). These wires carry information between the devices connected to the bus. Each device is recognized by a unique address and can operate as either a transmitter or receiver, depending on the function of the device. Devices can also be considered masters or slaves when performing data transfers. A master is a device that initiates a data transfer on the bus and generates the clock signals to permit that transfer. At that time, any device addressed is considered a slave.

Feature List

Up to 3 I2C.

Two-wire I2C serial interface: consists of a serial data line (SDA) and a serial clock (SCL).

Support master and slave mode.

Support 7/10-bit addressing mode.

Support standard mode (0 to 100Kb/s).

Support fast mode (less than or equal to 400Kb/s) or fast mode plus (less than or equal to 1000Kb/s).

Interrupt or polling mode operation.

Support GDMA.

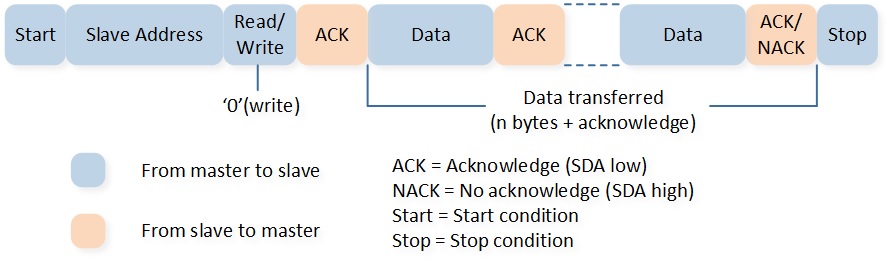

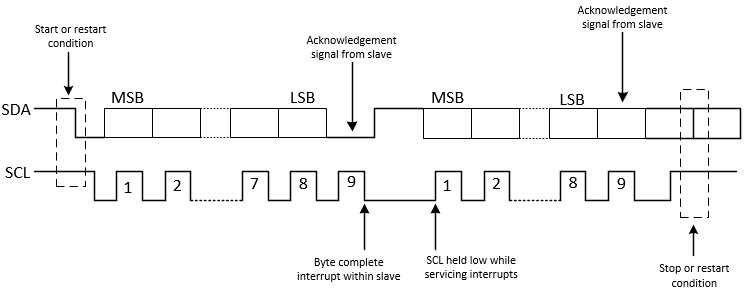

I2C Transfer Protocol

Each byte sent on the SDA line must be 8 bits. There is no limit to the number of bytes that can be sent per transfer, and each byte must be followed by a response bit. The most significant bit (MSB) of the data is transmitted first. If the slave needs to complete some other functions, such as an internal interrupt service routine, it can receive or send the next complete data byte. The clock line SCL can be kept low to force the master to enter the wait state. When the slave is ready to receive the next data byte and release the clock line SCL, the data transfer continues.

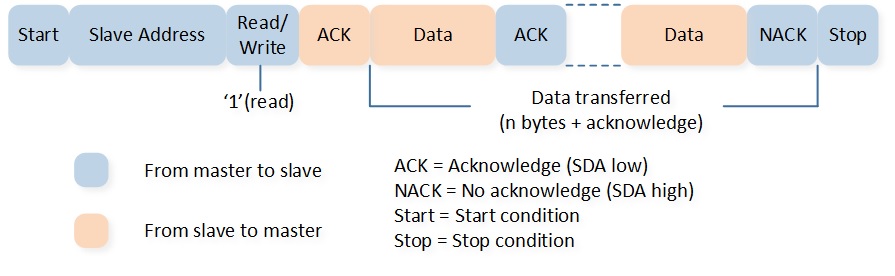

Master Mode

7-Bit Addressing Mode

Master Write

Master-transmitter transmits to slave-receiver with a 7-bit slave address. The transfer direction is not changed. All data is transmitted in byte format, with no limit on the number of bytes transferred per data transfer. After the master sends the address and read/write bit or the master transmits a byte of data to the slave, the slave-receiver must respond with the acknowledge signal (ACK). When a slave-receiver does not respond with an ACK pulse, the master aborts the transfer by issuing a stop condition. The slave must leave the SDA line high so that the master can abort the transfer.

Master Read

In the first response, master-transmitter becomes master-receiver, and slave-receiver becomes slave-transmitter, and the first response is still generated by the slave. If the master is receiving data, the master responds to the slave-transmitter with an acknowledge pulse after a byte of data has been received, except for the last byte. This (NACK) is the way the master-receiver notifies the slave-transmitter that this is the last byte. The slave-transmitter relinquishes the SDA line after detecting the no acknowledge (NACK) so that the master can issue a stop condition.

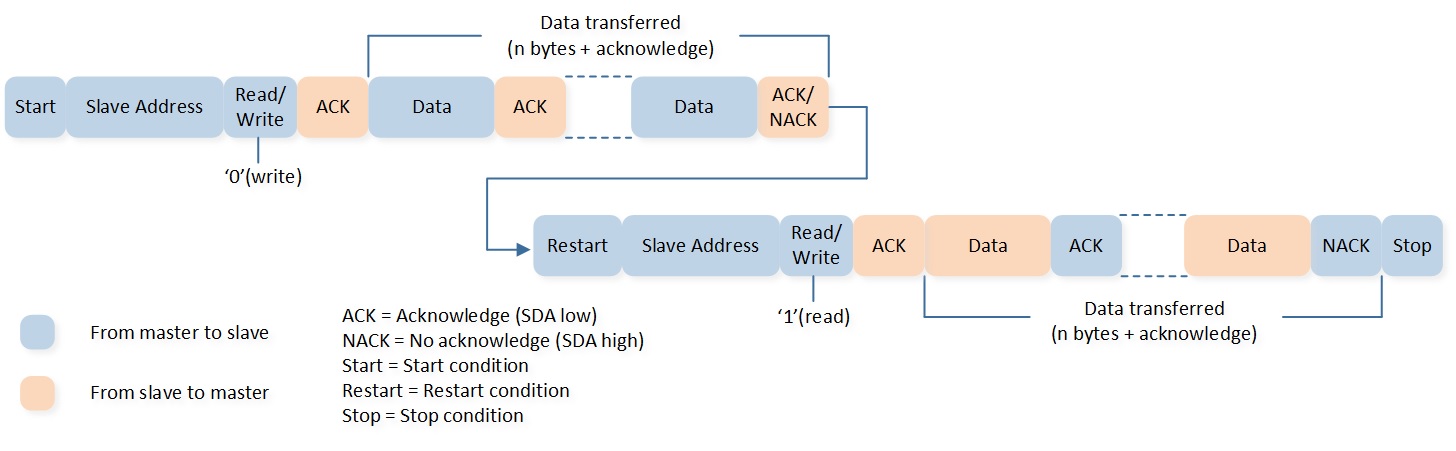

Master Repeat Read

When performing a write-before-read operation, both the start condition and the slave address are sent repeatedly, but the read/write bit is reversed.

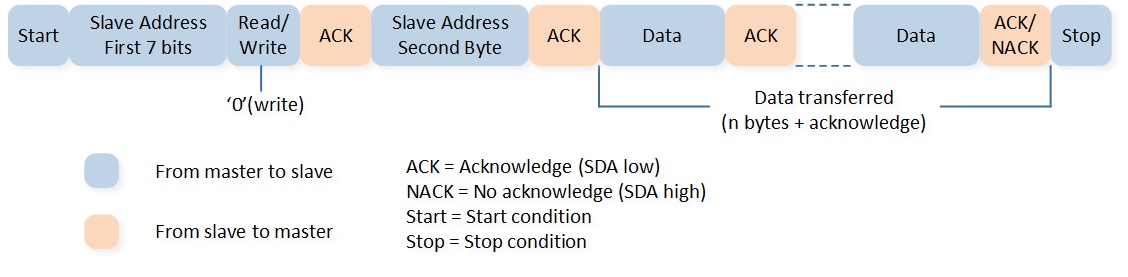

10-Bit Addressing Mode

Master Write

Master-transmitter transmits to slave-receiver with a 10-bit slave address. The transfer direction is not changed.

Master Read

Master-transmitter transmits to slave-receiver with a 10-bit slave address. The transfer direction is changed after the second read/write bit, master-transmitter becomes master-receiver, and slave-receiver becomes slave-transmitter.

Master Repeat Read

The master sends data to the slave and then reads data from the same slave. The transfer direction is changed after the second read/write bit.

I2C Clock Speed Setting Instructions

The I2C clock speed is related to the SCL rising time, which is affected by the pull-up resistor and capacitor. Users can configure the variable I2C_RisingTimeNs to calibrate the I2C clock speed. The default value of I2C_RisingTimeNs for RTL87x3D is 100, and the default value of I2C_RisingTimeNs for RTL87x3E and RTL87x3EP is 50. The following example demonstrates the calibration method of the I2C clock speed, taking the I2C source clock as 40MHz, the I2C clock speed as 400KHz, and the I2C_RisingTimeNs as 100.

Set the variable

I2C_RisingTimeNsto 100.Measure the I2C clock speed. For example, if the actual frequency measured is 411KHz, the period is: 1/411KHz = 2433 ns.

Calculate the actual value of

I2C_RisingTimeNs.SCL Low Time = SCL Low Period - SCL Falling Time + SCL Rising Time

SCL High Time = SCL High Period + SCL Falling Time

SCL Frequency = 1 / (SCL High Time + SCL Low Time)

According to the formulas a to c, SCL Period = SCL Low Period + SCL High Period + SCL Rising Time

SCL Low Period(ns) + SCL High Period(ns) = SCL Period(ns) -

I2C_RisingTimeNsconfigured in the APP = 2500 - 100 = 2400Actual

I2C_RisingTimeNs= Actual period - (SCL Low Period + SCL High Period) = 2433 - 2400 = 33Because the clock source of I2C is set to 40MHz, the precision of the I2C clock is 25ns. So the setting

I2C_RisingTimeNsneeds to be aligned to 25ns.

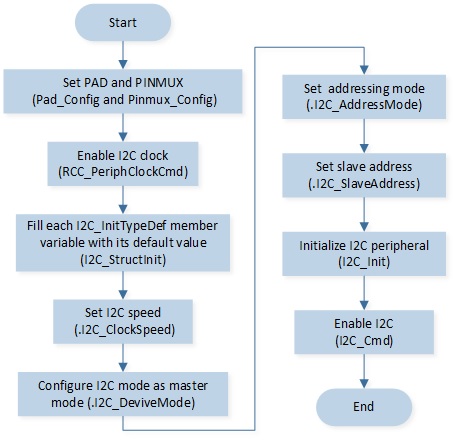

Master Mode Initialization Flow

I2C master mode initialization flow is shown in the following figure.

The codes below demonstrate the I2C master mode initialization flow.

void driver_i2c_init(void)

{

RCC_PeriphClockCmd(APBPeriph_I2C1, APBPeriph_I2C1_CLOCK, ENABLE);

I2C_InitTypeDef I2C_InitStructure;

I2C_StructInit(&I2C_InitStructure);

I2C_InitStructure.I2C_ClockSpeed = 400000;

I2C_InitStructure.I2C_DeviveMode = I2C_DeviveMode_Master;

I2C_InitStructure.I2C_AddressMode = I2C_AddressMode_7BIT;

I2C_InitStructure.I2C_SlaveAddress = ADDR;

I2C_InitStructure.I2C_Ack = I2C_Ack_Enable;

I2C_Init(I2C1, &I2C_InitStructure);

I2C_Cmd(I2C1, ENABLE);

}

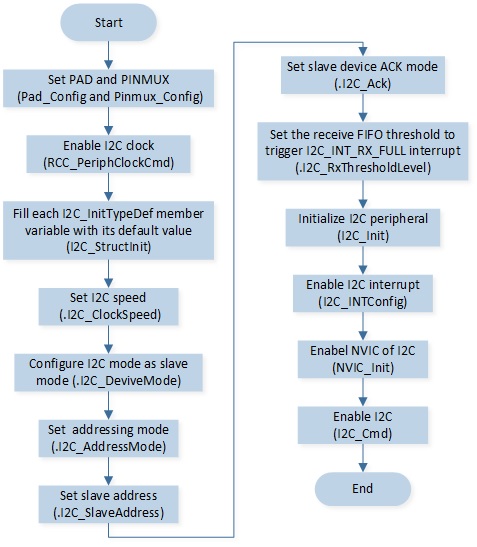

Slave Mode Initialization Flow

I2C slave mode initialization flow is shown in the following figure.

The codes below demonstrate the I2C slave mode initialization flow.

RCC_PeriphClockCmd(APBPeriph_I2C1, APBPeriph_I2C1_CLOCK, ENABLE);

I2C_InitTypeDef I2C_InitStructure;

I2C_StructInit(&I2C_InitStructure);

I2C_InitStructure.I2C_ClockSpeed = 100000;

I2C_InitStructure.I2C_DeviveMode = I2C_DeviveMode_Slave;

I2C_InitStructure.I2C_AddressMode = I2C_AddressMode_7BIT;

I2C_InitStructure.I2C_SlaveAddress = 0x50;

I2C_InitStructure.I2C_Ack = I2C_Ack_Enable;

I2C_Init(I2C1, &I2C_InitStructure);

/* Config I2C interrupt */

I2C_INTConfig(I2C1, I2C_INT_RD_REQ | I2C_INT_RX_FULL | I2C_INT_STOP_DET, ENABLE);

NVIC_InitTypeDef NVIC_InitStruct;

NVIC_InitStruct.NVIC_IRQChannel = I2C1_IRQn;

NVIC_InitStruct.NVIC_IRQChannelPriority = 3;

NVIC_InitStruct.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStruct);

I2C_Cmd(I2C1, ENABLE);

Master Write

The codes below demonstrate the operation flow of I2C sending data in master mode.

uint8_t I2C_WriteBuf[16] = {0xaa, 0xbb, 0x66, 0x68, 0x77, 0x88};

if (I2C_Success != I2C_MasterWrite(I2C1, I2C_WriteBuf, 6))

{

IO_PRINT_ERROR0("i2c_mw_demo: Send failed");

//Check Event

if (I2C_CheckEvent(I2C1, ABRT_7B_ADDR_NOACK) == SET)

{

IO_PRINT_ERROR0("i2c_mw_demo: Wrong addr");

}

if (I2C_CheckEvent(I2C1, ABRT_GCALL_NOACK) == SET)

{

IO_PRINT_ERROR0("i2c_mw_demo: General call nack");

}

I2C_SendCmd(I2C1, I2C_WRITE_CMD, 0, I2C_STOP_ENABLE);

I2C_Cmd(I2C1, DISABLE);

I2C_Cmd(I2C1, ENABLE);

I2C_MasterWrite(I2C1, I2C_WriteBuf, 6);

}

Master Repeat Read

The codes below demonstrate the operation flow of I2C send and receive data in master mode.

uint8_t I2C_WriteBuf[16] = {0xaa, 0xbb, 0x66, 0x68, 0x77, 0x88};

uint8_t I2C_ReadBuf[16] = {0, 0, 0, 0};

if (I2C_Success != I2C_RepeatRead(I2C1, I2C_WriteBuf, 2, I2C_ReadBuf, 4))

{

IO_PRINT_ERROR0("i2c_polling_demo: Send failed");

//Check Event

if (I2C_CheckEvent(I2C1, ABRT_7B_ADDR_NOACK) == SET)

{

IO_PRINT_ERROR0("i2c_polling_demo: Wrong addr");

}

if (I2C_CheckEvent(I2C1, ABRT_GCALL_NOACK) == SET)

{

IO_PRINT_ERROR0("i2c_polling_demo: General call nack");

}

}

SPI

SPI Demo Code Support List

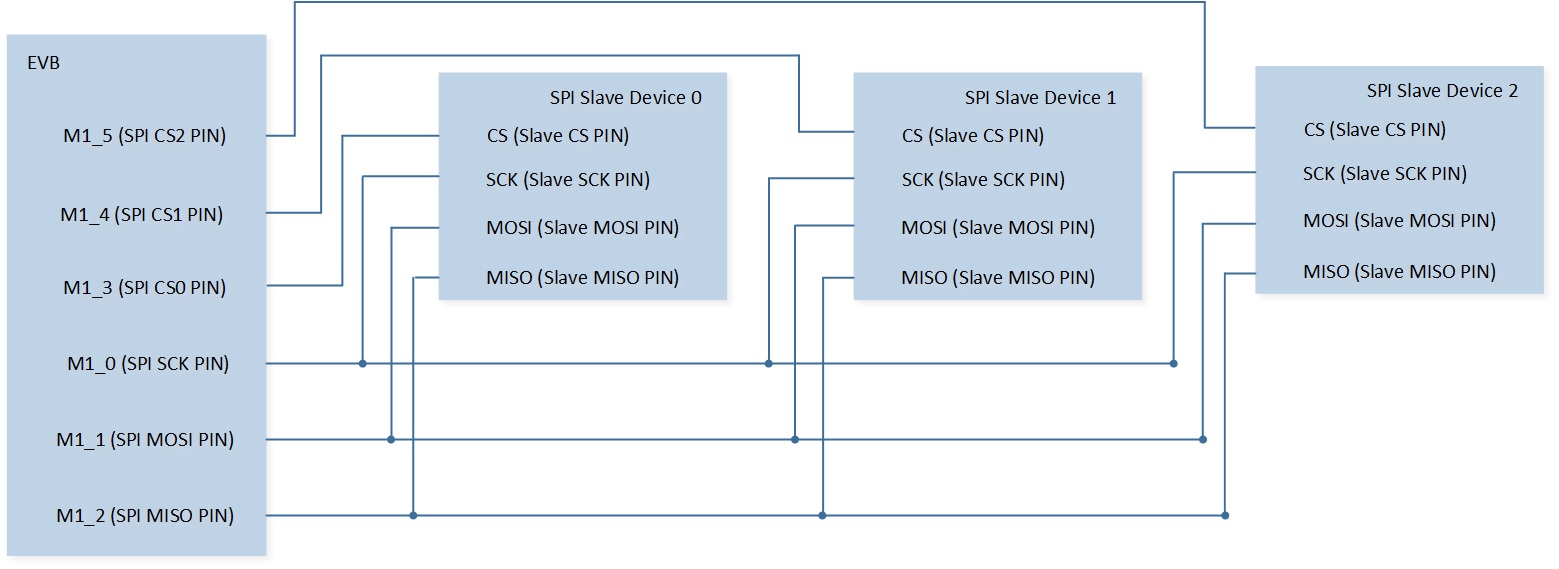

Demo 1 |

spi_switchcs_demo.c |

|---|---|

Sample Purpose |

Demonstrate how SPI dynamically switches CS signals. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in SPI Demo 1 Hardware Connection Diagram. Connect M1_3 to CS of SPI slave device 0, connect M1_4 to CS of SPI slave device 1, connect M1_5 to CS of SPI slave device 2, connect M1_0 to SCK of SPI slave device 0/1/2, connect M1_1 to MISO of SPI slave device 0/1/2, and connect M1_2 to MOSI of SPI slave device 0/1/2. |

SPI CS0 Pin Definition |

|

SPI CS1 Pin Definition |

|

SPI CS2 Pin Definition |

|

SPI SCK Pin Definition |

|

SPI MOSI Pin Definition |

|

SPI MISO Pin Definition |

|

SPI ID |

SPI1 |

Mode |

Master |

Speed |

400000 |

Data Size |

8-Bit |

Expected Result |

1. Press the reset button on the EVB. The data in array |

Demo 2 |

spi_master_eeprom_mode_demo.c |

|---|---|

Sample Purpose |

Demonstrate how SPI receives data with EEPROM mode by GDMA in master mode. |

File Path |

|

Function Entry |

|

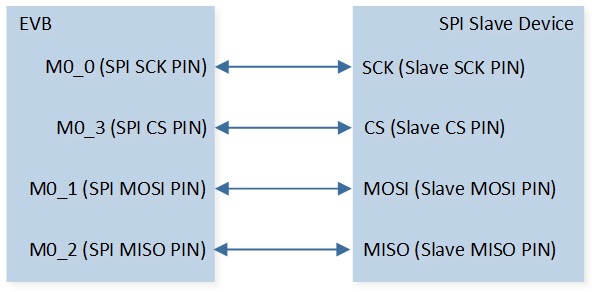

Hardware Connection |

As shown in SPI Demo 2/6 Hardware Connection Diagram. Connect M0_3 to CS of SPI slave device, connect M0_0 to SCK of SPI slave device, connect M0_1 to MISO of SPI slave device, and connect M0_2 to MOSI of SPI slave device. |

SPI CS Pin Definition |

|

SPI SCK Pin Definition |

|

SPI MOSI Pin Definition |

|

SPI MISO Pin Definition |

|

SPI ID |

SPI1 |

Mode |

Master |

Speed |

400000 |

Data Size |

8-Bit |

Expected Result |

Print string ‘spi_master_rx_dma_handler’ and the received data in Debug Analyzer. |

Demo 3 |

external_flash.c |

|---|---|

Sample Purpose |

Demonstrate how the chip communicates with external flash by SPI. |

File Path |

|

Function Entry |

|

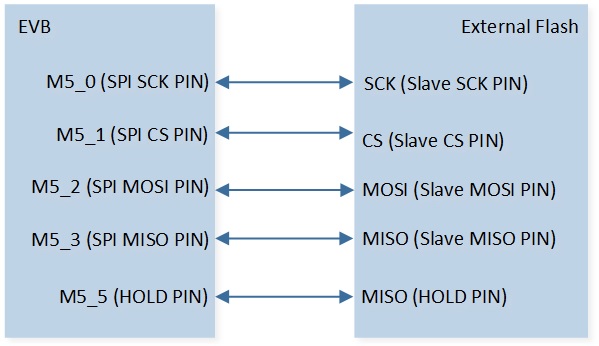

Hardware Connection |

As shown in SPI Demo 3 Hardware Connection Diagram. Connect M5_1 to CS of external flash, connect M5_0 to SCK of external flash, connect M5_3 to MISO of external flash, and connect M5_2 to MOSI of external flash, connect M5_5 to HOLD of external flash. |

SPI CS Pin Definition |

|

SPI SCK Pin Definition |

|

SPI MOSI Pin Definition |

|

SPI MISO Pin Definition |

|

FLASH HOLD Pin Definition |

|

SPI ID |

SPI0 |

Mode |

Master |

Speed |

400000 |

Data Size |

8-Bit |

Expected Result |

1. Print string ‘flash_test_task: test_case 1 success’ in Debug Analyzer. |

Demo 4 |

spi_master_demo.c |

|---|---|

Sample Purpose |

Demonstrate how SPI sends data by polling and receives data by interrupt in master mode. |

File Path |

|

Function Entry |

|

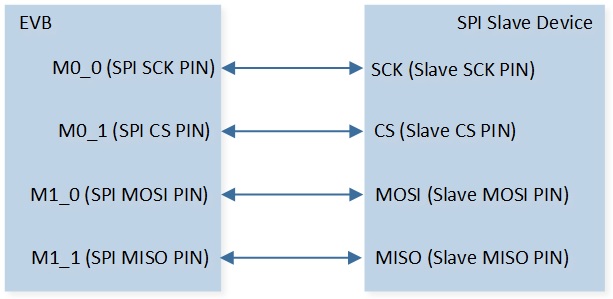

Hardware Connection |

As shown in SPI Demo 4 Hardware Connection Diagram. Connect M0_1 to CS of SPI slave device, connect M0_0 to SCK of SPI slave device, connect M1_0 to MISO of SPI slave device, and connect M1_1 to MOSI of SPI slave device. |

SPI CS Pin Definition |

|

SPI SCK Pin Definition |

|

SPI MOSI Pin Definition |

|

SPI MISO Pin Definition |

|

SPI ID |

SPI1 |

Mode |

Master |

Speed |

400000 |

Data Size |

8-Bit |

Expected Result |

1. Press the reset button on the EVB. The data in array |

Demo 5 |

spi_demo.c |

|---|---|

Sample Purpose |

Demonstrate how SPI sends and receives data by polling in master mode. |

File Path |

|

Function Entry |

|

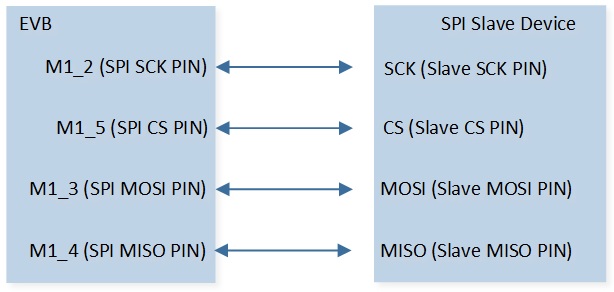

Hardware Connection |

As shown in SPI Demo 5 Hardware Connection Diagram. Connect M1_5 to CS of SPI slave device, connect M1_2 to SCK of SPI slave device, connect M1_3 to MISO of SPI slave device, and connect M1_4 to MOSI of SPI slave device. |

SPI CS Pin Definition |

|

SPI SCK Pin Definition |

|

SPI MOSI Pin Definition |

|

SPI MISO Pin Definition |

|

SPI ID |

SPI1 |

Mode |

Master |

Speed |

400000 |

Data Size |

8-Bit |

Expected Result |

1. Press the reset button on the EVB. The data in array |

Demo 6 |

spi_master_rx_only_mode_demo.c |

|---|---|

Sample Purpose |

Demonstrate how SPI receives data with receive only mode by GDMA in master mode. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in SPI Demo 2/6 Hardware Connection Diagram. Connect M0_3 to CS of SPI slave device, connect M0_0 to SCK of SPI slave device, connect M0_1 to MISO of SPI slave device, and connect M0_2 to MOSI of SPI slave device. |

SPI CS Pin Definition |

|

SPI SCK Pin Definition |

|

SPI MOSI Pin Definition |

|

SPI MISO Pin Definition |

|

SPI ID |

SPI1 |

Mode |

Master |

Speed |

400000 |

Data Size |

8-Bit |

Expected Result |

Print string ‘spi_master_rx_dma_handler’ and the received data in Debug Analyzer. |

Demo 7 |

spi_slave_demo.c |

|---|---|

Sample Purpose |

Demonstrate how SPI receives data by interrupt in slave mode. |

File Path |

|

Function Entry |

|

Hardware Connection |

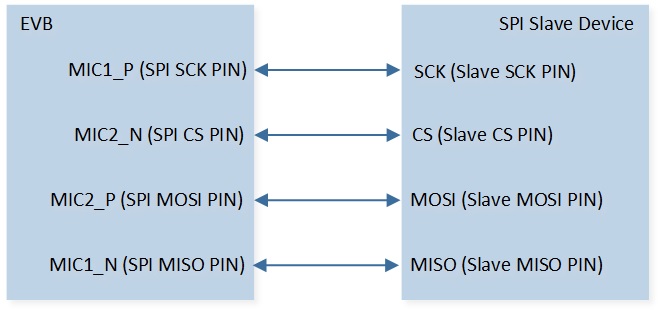

As shown in SPI Demo 7 Hardware Connection Diagram. Connect MIC2_N to CS of SPI master device, connect MIC1_P to SCK of SPI master device, connect MIC2_P to MISO of SPI master device, and connect MIC1_N to MOSI of SPI master device. |

SPI CS Pin Definition |

|

SPI SCK Pin Definition |

|

SPI MOSI Pin Definition |

|

SPI MISO Pin Definition |

|

SPI ID |

SPI0 |

Mode |

Slave |

Data Size |

8-Bit |

Expected Result |

Master device sends data to the chip. The chip stores the received data in array |

Demo 8 |

spi_slave_gpio_demo.c |

|---|---|

Sample Purpose |

Demonstrate how SPI sends data in slave mode by interrupt. |

File Path |

|

Function Entry |

|

Hardware Connection |

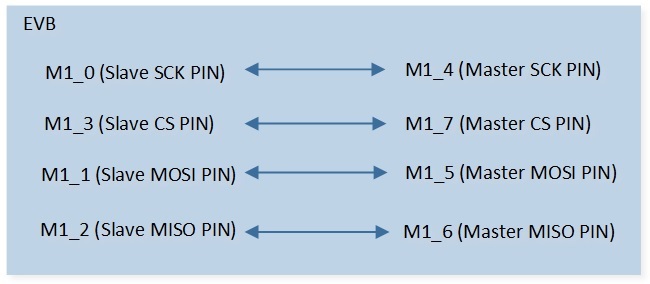

As shown in SPI Demo 8 Hardware Connection Diagram. Connect M1_4 to M1_0, connect M1_7 to M1_3, connect M1_5 to M1_2, connect M1_6 to M1_1, and connect M2_3 to M2_4. |

SPI0 CS Pin Definition |

|

SPI0 SCK Pin Definition |

|

SPI0 MOSI Pin Definition |

|

SPI0 MISO Pin Definition |

|

SPI1 CS Pin Definition |

|

SPI1 SCK Pin Definition |

|

SPI1 MOSI Pin Definition |

|

SPI1 MISO Pin Definition |

|

SPI ID |

SPI0 |

Mode |

SPI1 is master, SPI0 is slave. |

Speed |

100000 |

Data Size |

8-Bit |

Expected Result |

1. Master device sends data to slave. The slave stores the received data in array |

Demo 9 |

spi_slave_write_demo.c |

|---|---|

Sample Purpose |

Demonstrate how SPI sends data in slave mode by GDMA. |

File Path |

|

Function Entry |

|

Hardware Connection |

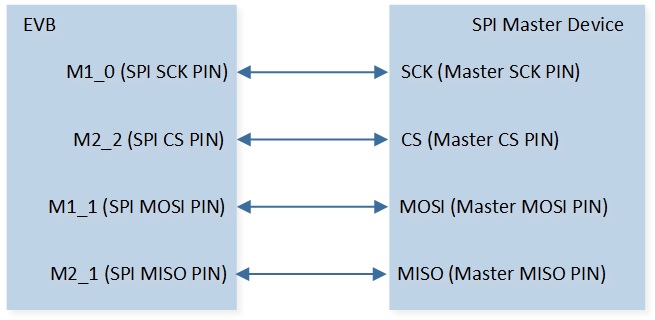

As shown in SPI Demo 9 Hardware Connection Diagram. Connect M2_2 to CS of SPI master device, connect M1_0 to SCK of SPI master device, connect M1_1 to MISO of SPI master device, and connect M2_1 to MOSI of SPI master device. |

SPI CS Pin Definition |

|

SPI SCK Pin Definition |

|

SPI MOSI Pin Definition |

|

SPI MISO Pin Definition |

|

SPI ID |

SPI0 |

Mode |

Slave |

Data Size |

8-Bit |

Expected Result |

1. The data in array sendbuf is sent to SPI master device and prints the string ‘spi_slave_tx_dma_handler’ in Debug Analyzer. |

Demo 10 |

spi0_hs_dma_demo.c |

|---|---|

Sample Purpose |

Demonstrate how SPI0 sends and receives data in high-speed mode. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in SPI Demo 10 Hardware Connection Diagram. Connect M1_2 to CS of SPI slave device, connect M1_3 to SCK of SPI slave device, connect M1_4 to MISO of SPI slave device, and connect M1_5 to MOSI of SPI slave device. |

SPI CS Pin Definition |

|

SPI SCK Pin Definition |

|

SPI MOSI Pin Definition |

|

SPI MISO Pin Definition |

|

SPI ID |

SPI0 |

Mode |

Master |

Speed |

40MHz |

Data Size |

8-Bit |

Expected Result |

1. Press the reset button on the EVB and the data in array |

Demo 11 |

spi2spi_auto_reload_dma.c |

|---|---|

Sample Purpose |

Demonstrate how SPI0 reads data and SPI1 sends data by GDMA. |

File Path |

|

Function Entry |

|

Hardware Connection |

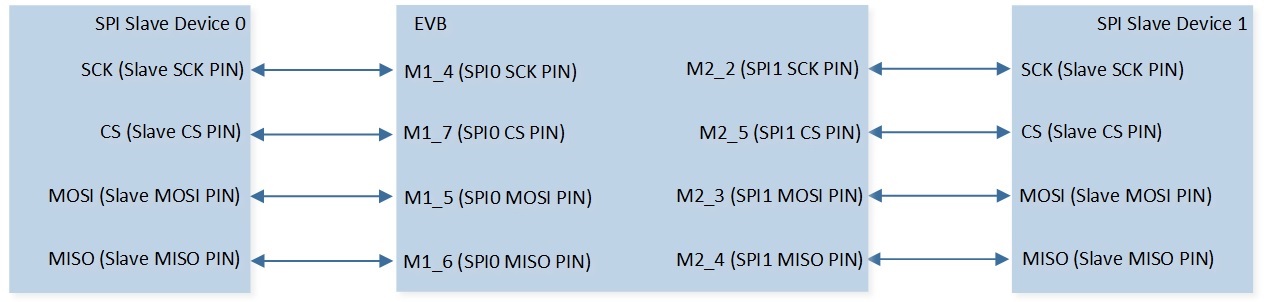

As shown in SPI Demo 11/12 Hardware Connection Diagram. Connect M1_7 to CS of SPI slave device 0, connect M1_4 to SCK of SPI slave device 0, connect M1_5 to MISO of SPI slave device 0, and connect M1_6 to MOSI of SPI slave device 0. Connect M2_5 to CS of SPI slave device 1, connect M2_2 to SCK of SPI slave device 1, connect M2_3 to MISO of SPI slave device 1, and connect M2_4 to MOSI of SPI slave device 1. |

SPI0 CS Pin Definition |

|

SPI0 SCK Pin Definition |

|

SPI0 MOSI Pin Definition |

|

SPI0 MISO Pin Definition |

|

SPI1 CS Pin Definition |

|

SPI1 SCK Pin Definition |

|

SPI1 MOSI Pin Definition |

|

SPI1 MISO Pin Definition |

|

SPI ID |

SPI0 |

Mode |

Master |

Speed |

400000 |

Data Size |

8-Bit |

Expected Result |

SPI0 reads data from SPI slave device 0 and SPI1 sends the same data to SPI slave device 1. |

Demo 12 |

spi2spi_dma_demo.c |

|---|---|

Sample Purpose |

Demonstrate how SPI0 reads data and SPI1 sends data by auto-reload GDMA. |

File Path |

|

Function Entry |

|

Hardware Connection |

As shown in SPI Demo 11/12 Hardware Connection Diagram. Connect M1_7 to CS of SPI slave device 0, connect M1_4 to SCK of SPI slave device 0, connect M1_5 to MISO of SPI slave device 0, and connect M1_6 to MOSI of SPI slave device 0. Connect M2_5 to CS of SPI slave device 1, connect M2_2 to SCK of SPI slave device 1, connect M2_3 to MISO of SPI slave device 1, and connect M2_4 to MOSI of SPI slave device 1. |

SPI0 CS Pin Definition |

|

SPI0 SCK Pin Definition |

|

SPI0 MOSI Pin Definition |

|

SPI0 MISO Pin Definition |

|

SPI1 CS Pin Definition |

|

SPI1 SCK Pin Definition |

|

SPI1 MOSI Pin Definition |

|

SPI1 MISO Pin Definition |

|

SPI ID |

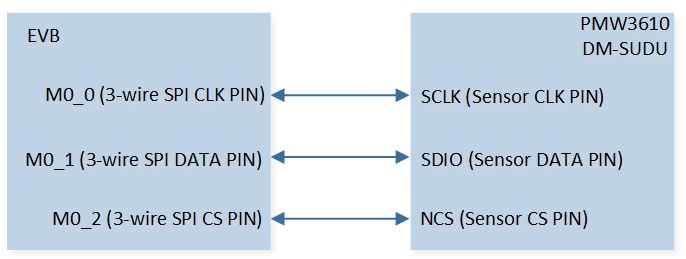

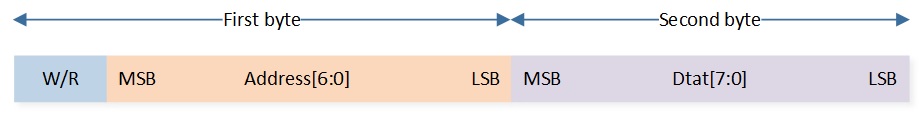

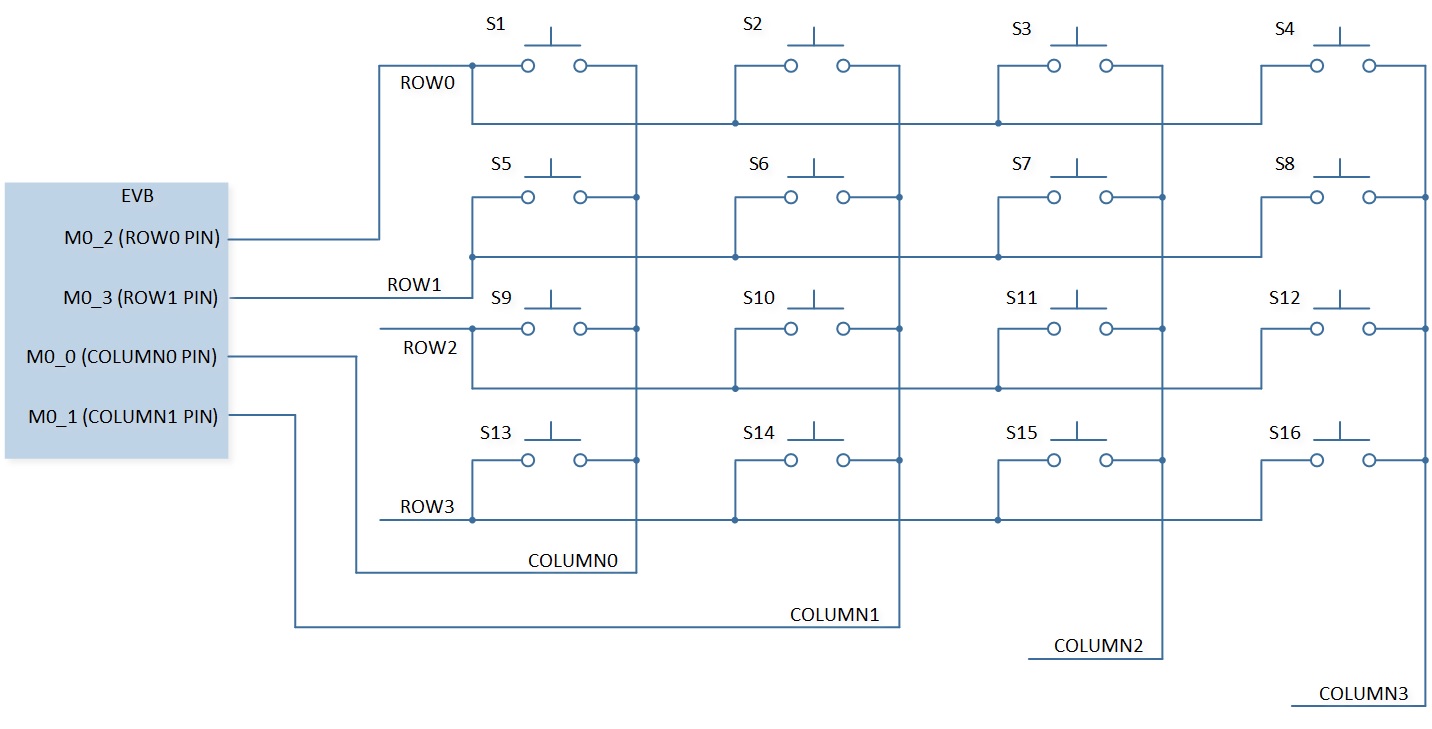

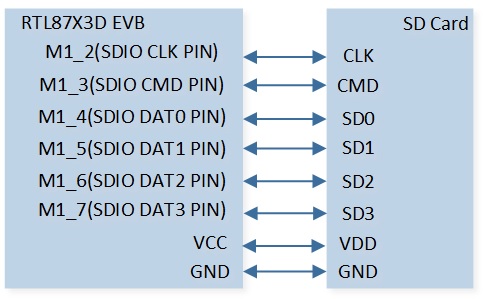

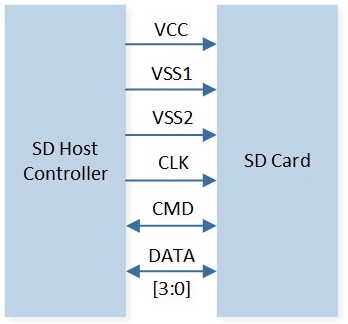

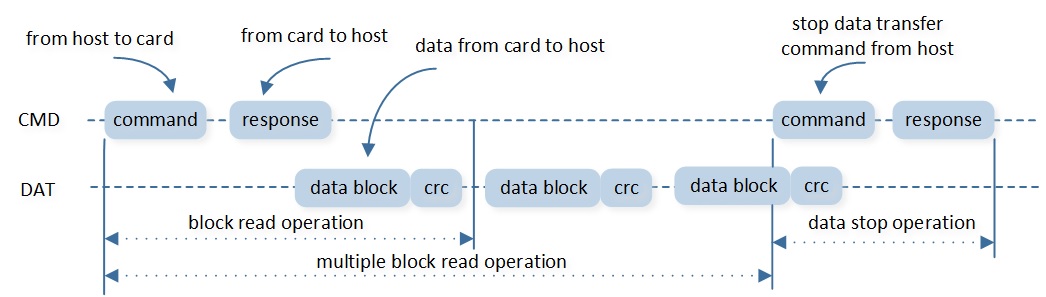

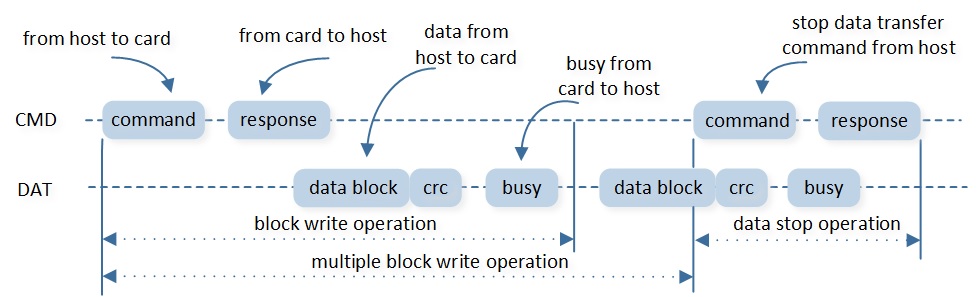

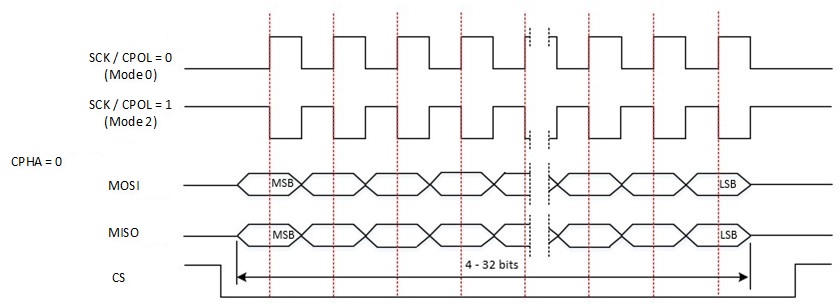

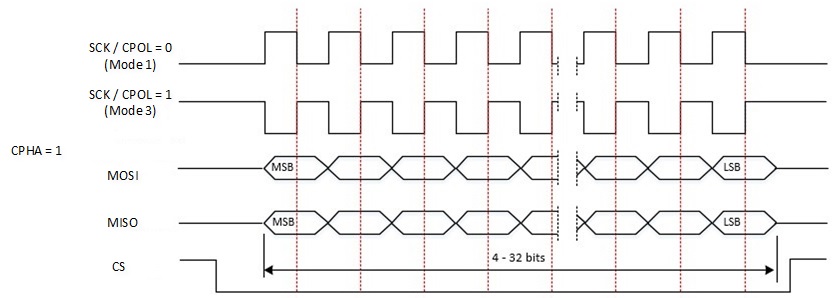

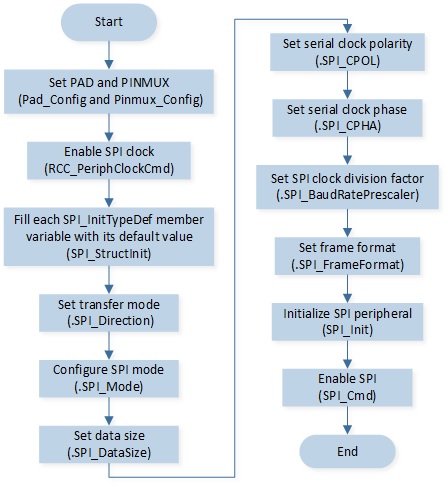

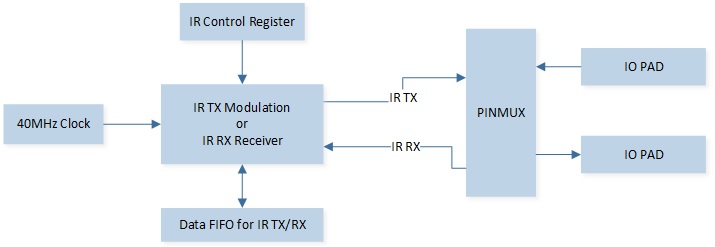

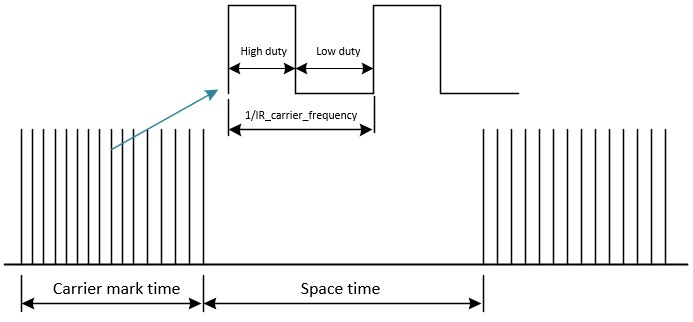

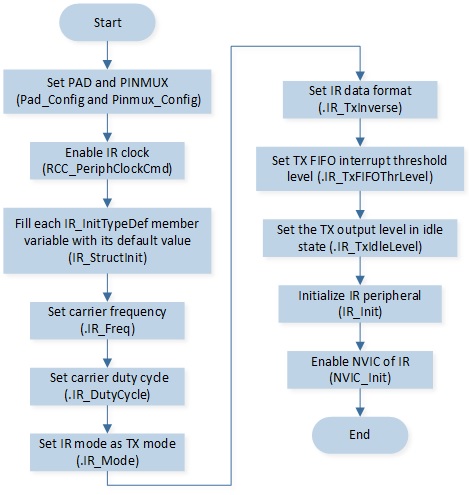

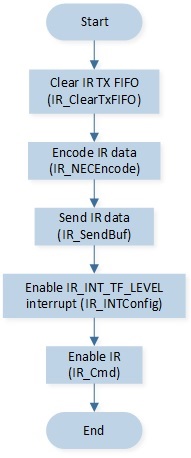

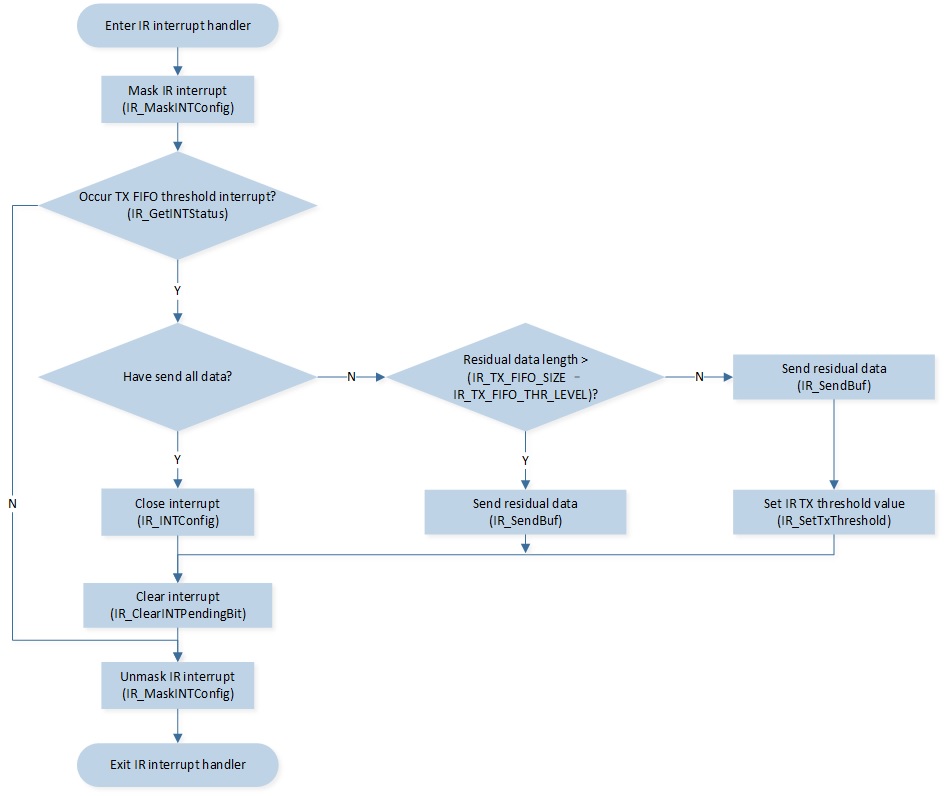

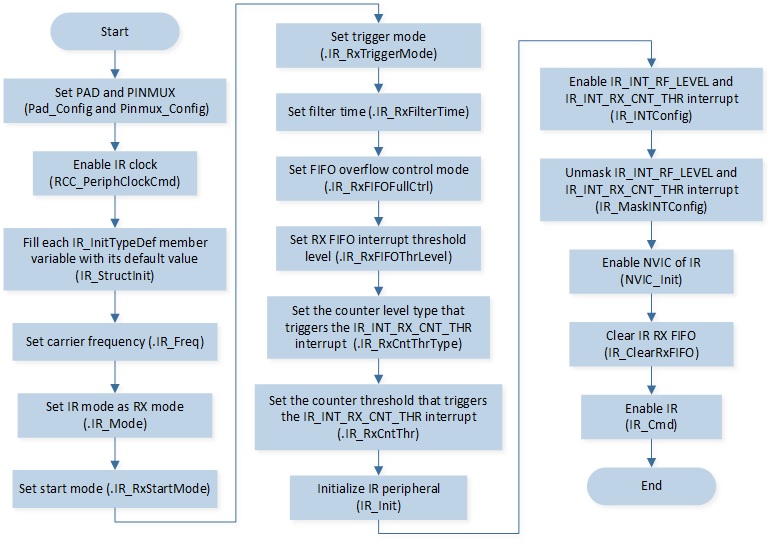

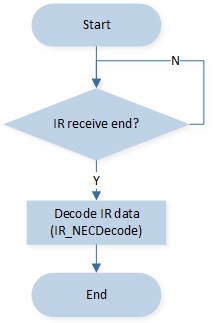

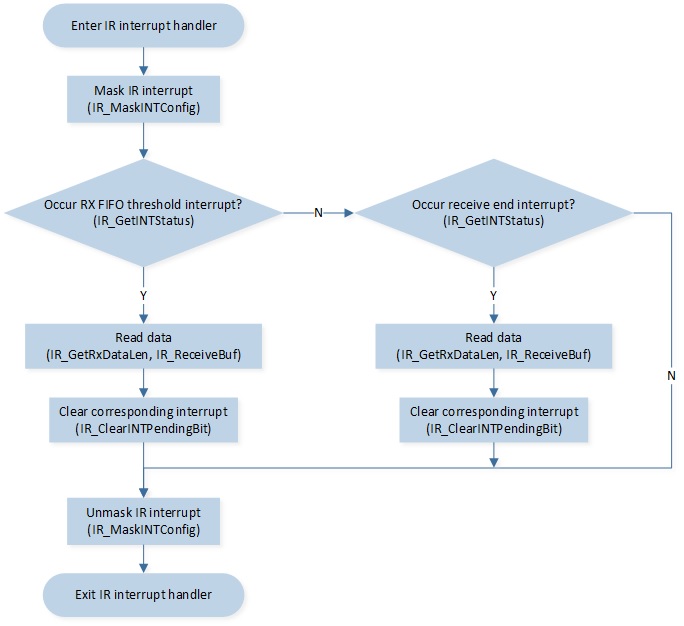

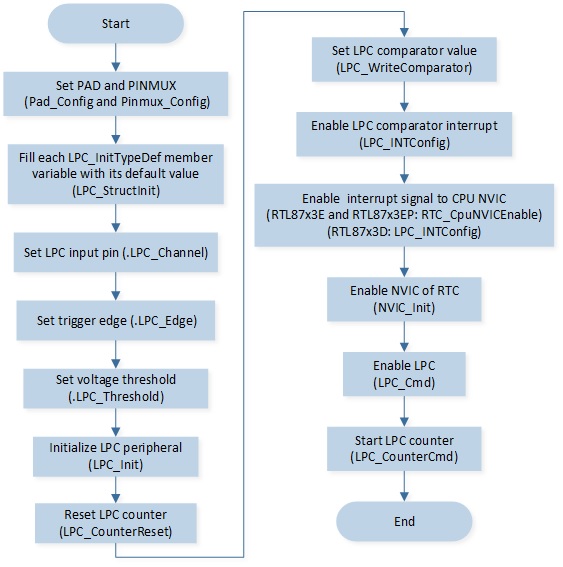

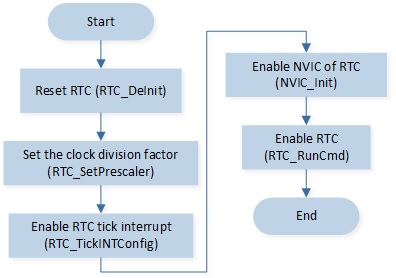

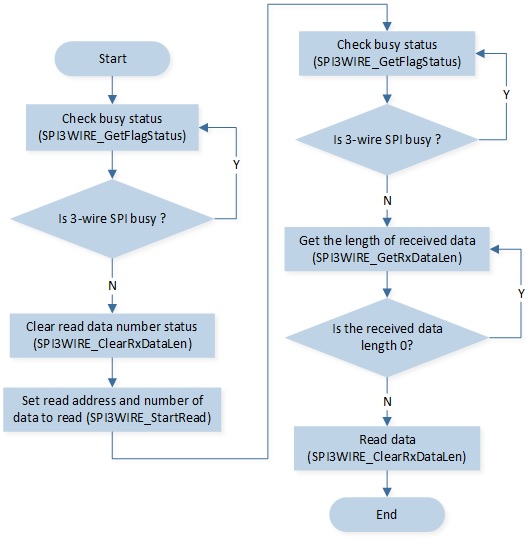

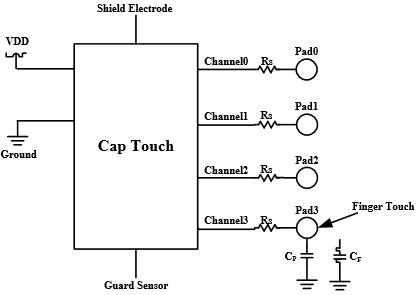

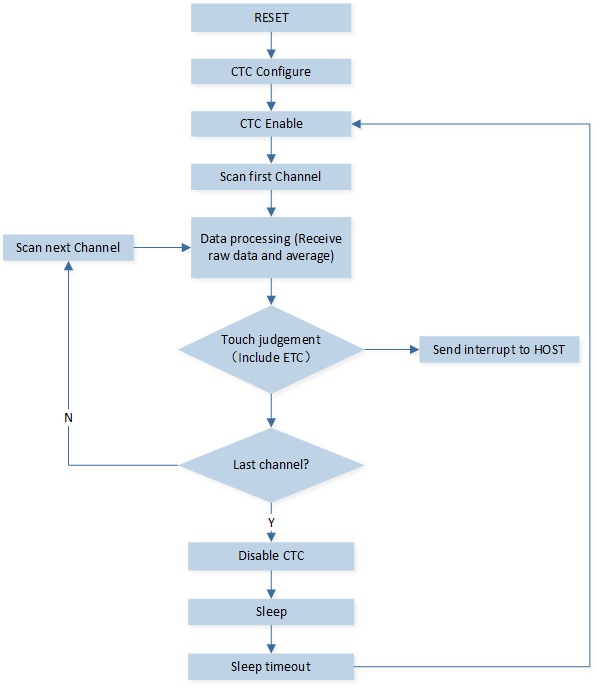

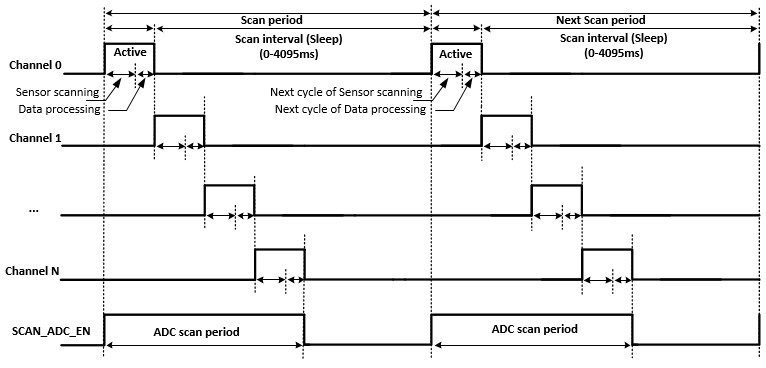

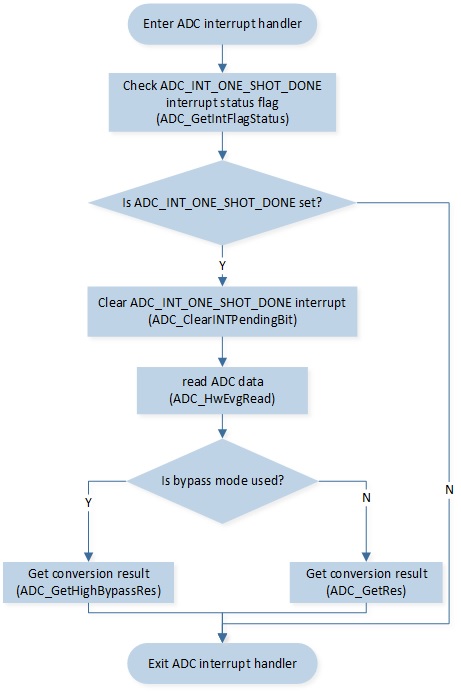

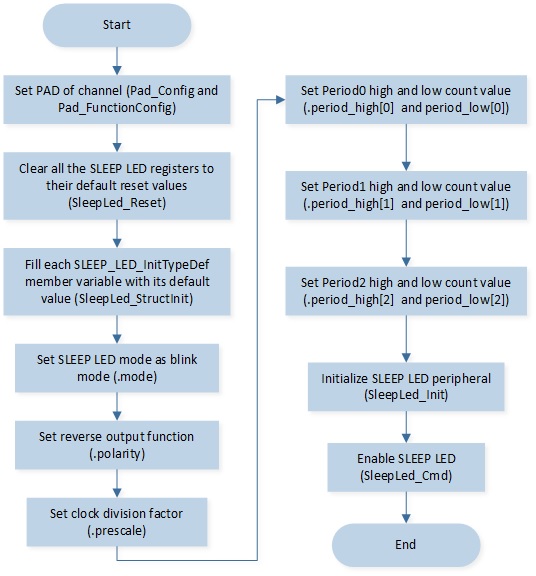

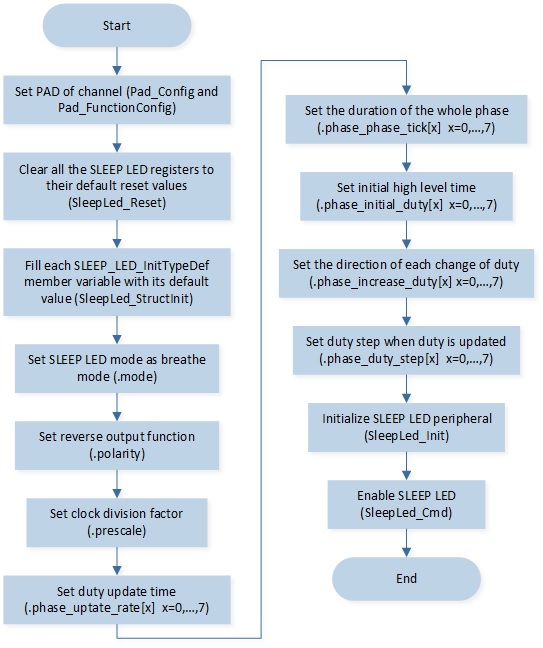

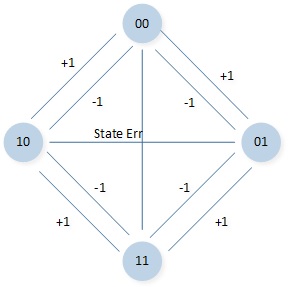

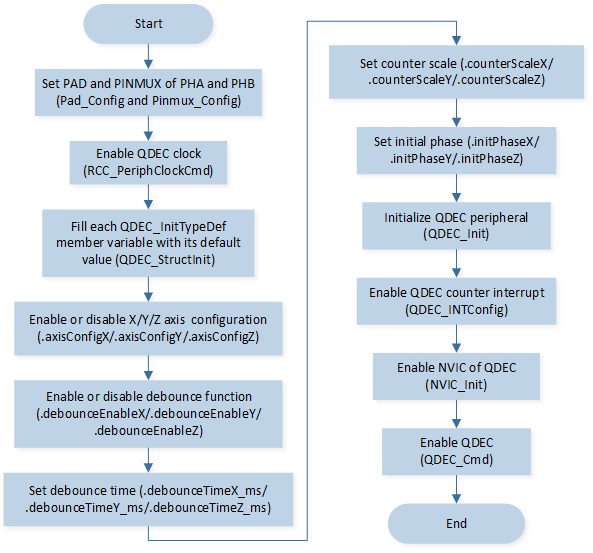

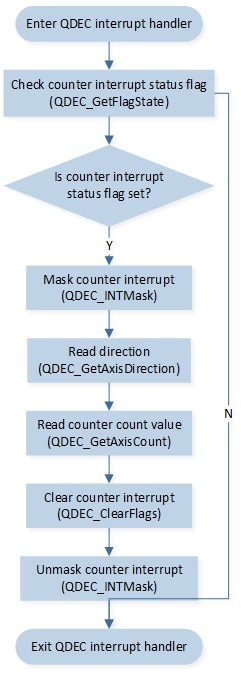

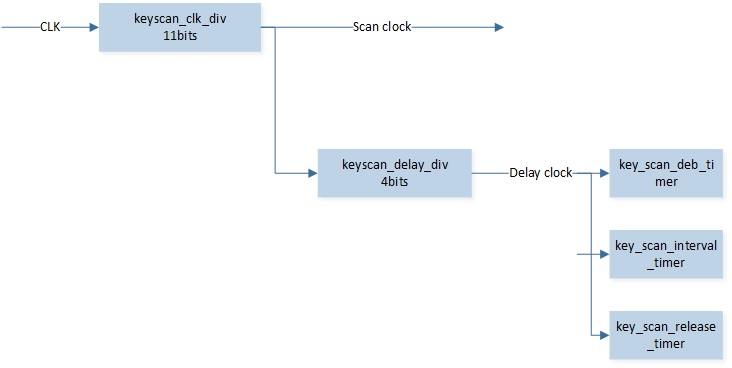

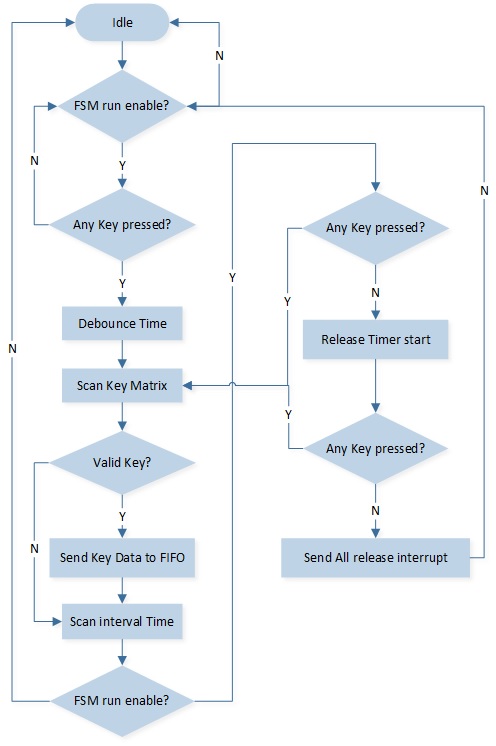

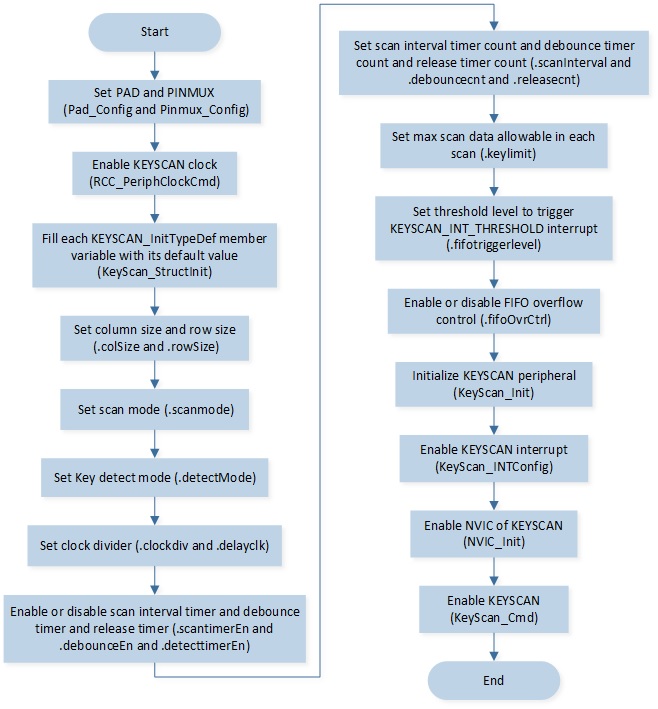

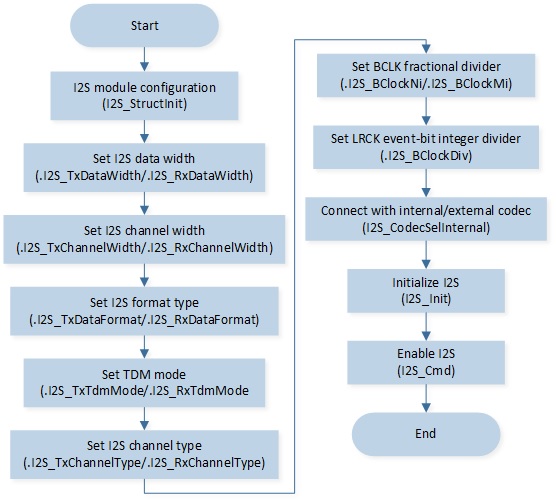

SPI0 |