SPI Master EEPROM and RX Only

This document introduces two SPI communication samples. The sample1 demonstrates how SPI receives data in EEPROM mode. The sample2 demonstrates how SPI receives data in receive-only mode. In both examples, SPI is configured as a master and operates in DMA mode. The chip reads data from the SPI slave.

Requirements

For hardware requirements, please refer to the Requirements.

Wiring

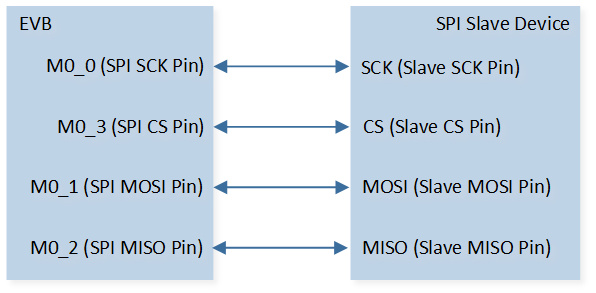

Connect P0_0 (master SCK) to SCK of SPI slave device, connect P0_1 (master MOSI) to MOSI of SPI slave device, connect P0_2 (master MISO) to MISO of SPI slave device, and connect P0_3 (master CS) to CS of SPI slave device. The hardware connection of SPI sample code is shown in the figure below.

SPI Sample Code Hardware Connection Diagram

Configurations

-

The following macros can be configured to modify pin definitions.

#define PIN_SPI_SCK P0_0#define PIN_SPI_MOSI P0_1#define PIN_SPI_MISO P0_2#define PIN_SPI_CS P0_3

-

The entry function are as follows, call this function in

main()to run this sample code. For more details, please refer to the Initialization.For sample 1, use the following entry function:

spi_master_eeprom_mode_demo();

For sample 2, use the following entry function:

spi_master_rx_only_mode_demo();

Building and Downloading

For building and downloading, please refer to the Building and Downloading.

Experimental Verification

Sample 1 Verification

Press the Reset button on the EVB, the 3 bytes data in the array

send_bufis sent to SPI TX FIFO.SPI will send 3 TX data frames in TX FIFO first. SPI does not read the data on MISO to RX FIFO when SPI sends these three data frames.

After the 3 bytes data have been sent, SPI would send 0x0 at MOSI and start reading the data to RX FIFO automatically, the data length is 16.

-

When SPI has read 16 data frames, it enters the GDMA interrupt and prints the received data in Debug Analyzer.

spi_master_rx_dma_handler spi_master_rx_dma_handler: DMA master read_buf[0] 0x%x ... spi_master_rx_dma_handler: DMA master read_buf[15] 0x%x

Sample 2 Verification

Press the Reset button on the EVB, the one bytes data in the array

send_bufis sent to SPI TX FIFO.SPI will send dummy data at MOSI automatically and start reading the data to RX FIFO, the dummy data length is 16.

-

When SPI has read 16 data frames, it enters the GDMA interrupt and prints the received data in Debug Analyzer.

spi_master_rx_dma_handler spi_master_rx_dma_handler: DMA master read_buf[0] 0x%x ... spi_master_rx_dma_handler: DMA master read_buf[15] 0x%x

Code Overview

Source Code Directory

For both samples, please refer to the Source Code Directory for the project directory.

Sample 1 source code:

Source code directory:

sdk\src\sample\io_demo\spi\eeprom\spi_master_eeprom_mode_demo.c.

Sample 2 source code:

Source code directory:

sdk\src\sample\io_demo\spi\receive_only\spi_master_rx_only_mode_demo.c.

RX DMA Initialization Flow

The initialization flow for peripherals can refer to Initialization Flow.

The SPI RX DMA initialization flow requires first initializing the SPI peripheral, followed by RX DMA initialization. The SPI initialization flow can refer to SPI Initialization Flow Chart. The SPI RX DMA initialization flow can refer to SPI RX DMA Initialization Flow Chart.

-

Call

Pad_Config()andPinmux_Config()to initialize the pin.static void board_spi_init(void) { Pinmux_Config(PIN_SPI_SCK, SPI_CLK_MASTER); Pinmux_Config(PIN_SPI_MOSI, SPI_MO_MASTER); Pinmux_Config(PIN_SPI_MISO, SPI_MI_MASTER); Pinmux_Config(PIN_SPI_CS, SPI_SS_N_0_MASTER); Pad_Config(PIN_SPI_SCK, PAD_PINMUX_MODE, PAD_IS_PWRON, PAD_PULL_NONE, PAD_OUT_DISABLE, PAD_OUT_HIGH); Pad_Config(PIN_SPI_MOSI, PAD_PINMUX_MODE, PAD_IS_PWRON, PAD_PULL_NONE, PAD_OUT_DISABLE, PAD_OUT_HIGH); Pad_Config(PIN_SPI_MISO, PAD_PINMUX_MODE, PAD_IS_PWRON, PAD_PULL_NONE, PAD_OUT_DISABLE, PAD_OUT_HIGH); Pad_Config(PIN_SPI_CS, PAD_PINMUX_MODE, PAD_IS_PWRON, PAD_PULL_NONE, PAD_OUT_DISABLE, PAD_OUT_HIGH); }

Call

RCC_PeriphClockCmd()to enable the SPI clock and function.-

Initialize the SPI peripheral:

Define the

SPI_InitTypeDeftypeSPI_InitStructure, and callSPI_StructInit()to pre-fillSPI_InitStructurewith default values.Modify the

SPI_InitStructureparameters as needed. The SPI initialization parameter configuration is shown in the table below.Call

SPI_Init()to initialize the SPI peripheral.

SPI Initialization Parameters SPI Hardware Parameters

Setting in the

SPI_InitStructureSPI

Direction

Device Role (SPI Master or SPI Slave)

Data Frame Size

Clock Polarity

Clock Phase

Clock Div

100

RX Number of Data Frames

16

RX Water Level

1

Call

SPI_Cmd()to enable SPI.Call

RCC_PeriphClockCmd()to enable the GDMA clock and function.Call

GDMA_channel_requestto request a free GDMA channel and register the GDMA interrupt handler.-

Initialize the GDMA peripheral:

Define the

GDMA_InitTypeDeftypeGDMA_InitStruct, and callGDMA_StructInit()to pre-fillGDMA_InitStructwith default values.Modify the

GDMA_InitStructparameters as needed. The GDMA initialization parameter configuration is shown in the table below.Call

GDMA_Init()to initialize the GDMA peripheral.

GDMA Initialization Parameters GDMA Hardware Parameters

Setting in the

GDMA_InitStructGDMA

Channel Num

SPI_MASTER_RX_DMA_CHANNEL_NUMTransfer Direction

Buffer Size

TEST_SIZESource Address Increment or Decrement

Destination Address Increment or Decrement

Source Data Size

Destination Data Size

Source Burst Transaction Length

Destination Burst Transaction Length

Source Address

SPI1->DRDestination Address

read_bufSource Handshake

GDMA_Handshake_SPI1_RX Call

GDMA_INTConfig()to enable GDMA transfer complete interruptGDMA_INT_Transfer.Call

NVIC_Init()to enable NVIC of GDMA.

Functional Implementation

Master Receive Data by DMA

Call

SPI_SetReadLen()to config the length of data which want to read.Call

SPI_GDMACmd()to disable and then enable SPI GDMA RX Function.Call

GDMA_Cmd()to enable DMA transfers.Call

SPI_SendBuffer()to send the data insend_bufto TX FIFO, then SPI would send dummy data at MOSI and start reading the data to RX FIFO automatically.When GDMA transfer is completed, transfer complete interrupt is triggered. Then call

GDMA_ClearINTPendingBit()to clearGDMA_INT_Transferinterrupt.